From Wikipedia, the free encyclopedia

«Superscaler» redirects here. For the Sega arcade system board, see Sega Super Scaler.

A superscalar processor is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor.[1] In contrast to a scalar processor, which can execute at most one single instruction per clock cycle, a superscalar processor can execute more than one instruction during a clock cycle by simultaneously dispatching multiple instructions to different execution units on the processor. It therefore allows more throughput (the number of instructions that can be executed in a unit of time) than would otherwise be possible at a given clock rate. Each execution unit is not a separate processor (or a core if the processor is a multi-core processor), but an execution resource within a single CPU such as an arithmetic logic unit.

While a superscalar CPU is typically also pipelined, superscalar and pipelining execution are considered different performance enhancement techniques. The former executes multiple instructions in parallel by using multiple execution units, whereas the latter executes multiple instructions in the same execution unit in parallel by dividing the execution unit into different phases.

The superscalar technique is traditionally associated with several identifying characteristics (within a given CPU):

- Instructions are issued from a sequential instruction stream

- The CPU dynamically checks for data dependencies between instructions at run time (versus software checking at compile time)

- The CPU can execute multiple instructions per clock cycle

History[edit]

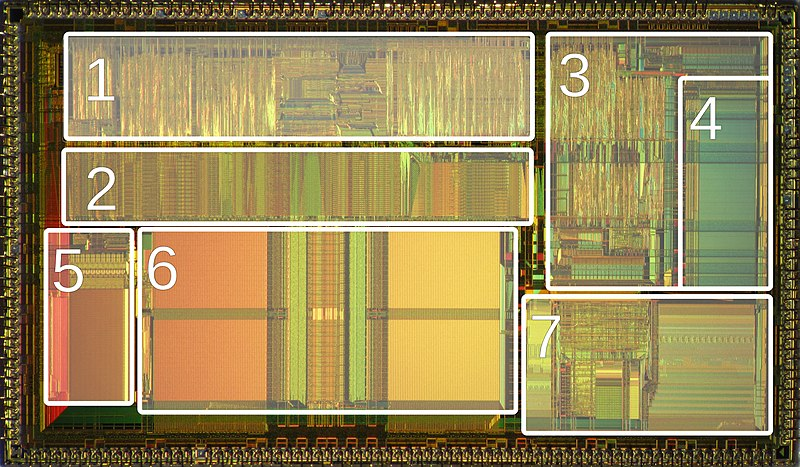

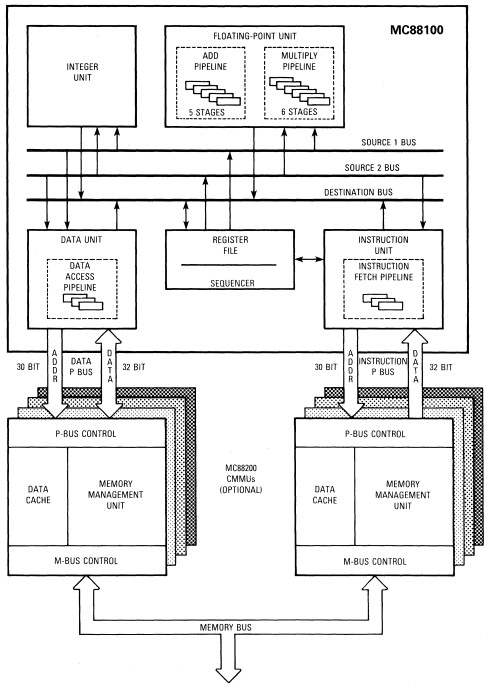

Seymour Cray’s CDC 6600 from 1964 is often mentioned as the first superscalar design. The 1967 IBM System/360 Model 91 was another superscalar mainframe. The Motorola MC88100 (1988), the Intel i960CA (1989) and the AMD 29000-series 29050 (1990) microprocessors were the first commercial single-chip superscalar microprocessors. RISC microprocessors like these were the first to have superscalar execution, because RISC architectures free transistors and die area which can be used to include multiple execution units (this was why RISC designs were faster than CISC designs through the 1980s and into the 1990s).

Except for CPUs used in low-power applications, embedded systems, and battery-powered devices, essentially all general-purpose CPUs developed since about 1998 are superscalar.

The P5 Pentium was the first superscalar x86 processor; the Nx586, P6 Pentium Pro and AMD K5 were among the first designs which decode x86-instructions asynchronously into dynamic microcode-like micro-op sequences prior to actual execution on a superscalar microarchitecture; this opened up for dynamic scheduling of buffered partial instructions and enabled more parallelism to be extracted compared to the more rigid methods used in the simpler P5 Pentium; it also simplified speculative execution and allowed higher clock frequencies compared to designs such as the advanced Cyrix 6×86.

Scalar to superscalar[edit]

The simplest processors are scalar processors. Each instruction executed by a scalar processor typically manipulates one or two data items at a time. By contrast, each instruction executed by a vector processor operates simultaneously on many data items. An analogy is the difference between scalar and vector arithmetic. A superscalar processor is a mixture of the two. Each instruction processes one data item, but there are multiple execution units within each CPU thus multiple instructions can be processing separate data items concurrently.

Superscalar CPU design emphasizes improving the instruction dispatcher accuracy, and allowing it to keep the multiple execution units in use at all times. This has become increasingly important as the number of units has increased. While early superscalar CPUs would have two ALUs and a single FPU, a later design such as the PowerPC 970 includes four ALUs, two FPUs, and two SIMD units. If the dispatcher is ineffective at keeping all of these units fed with instructions, the performance of the system will be no better than that of a simpler, cheaper design.

A superscalar processor usually sustains an execution rate in excess of one instruction per machine cycle. But merely processing multiple instructions concurrently does not make an architecture superscalar, since pipelined, multiprocessor or multi-core architectures also achieve that, but with different methods.

In a superscalar CPU the dispatcher reads instructions from memory and decides which ones can be run in parallel, dispatching each to one of the several execution units contained inside a single CPU. Therefore, a superscalar processor can be envisioned having multiple parallel pipelines, each of which is processing instructions simultaneously from a single instruction thread.

Limitations[edit]

Available performance improvement from superscalar techniques is limited by three key areas:

- The degree of intrinsic parallelism in the instruction stream (instructions requiring the same computational resources from the CPU)

- The complexity and time cost of dependency checking logic and register renaming circuitry

- The branch instruction processing

Existing binary executable programs have varying degrees of intrinsic parallelism. In some cases instructions are not dependent on each other and can be executed simultaneously. In other cases they are inter-dependent: one instruction impacts either resources or results of the other. The instructions a = b + c; d = e + f can be run in parallel because none of the results depend on other calculations. However, the instructions a = b + c; b = e + f might not be runnable in parallel, depending on the order in which the instructions complete while they move through the units.

Although the instruction stream may contain no inter-instruction dependencies, a superscalar CPU must nonetheless check for that possibility, since there is no assurance otherwise and failure to detect a dependency would produce incorrect results.

No matter how advanced the semiconductor process or how fast the switching speed, this places a practical limit on how many instructions can be simultaneously dispatched. While process advances will allow ever greater numbers of execution units (e.g. ALUs), the burden of checking instruction dependencies grows rapidly, as does the complexity of register renaming circuitry to mitigate some dependencies. Collectively the power consumption, complexity and gate delay costs limit the achievable superscalar speedup.

However even given infinitely fast dependency checking logic on an otherwise conventional superscalar CPU, if the instruction stream itself has many dependencies, this would also limit the possible speedup. Thus the degree of intrinsic parallelism in the code stream forms a second limitation.

Alternatives[edit]

Collectively, these limits drive investigation into alternative architectural changes such as very long instruction word (VLIW), explicitly parallel instruction computing (EPIC), simultaneous multithreading (SMT), and multi-core computing.

With VLIW, the burdensome task of dependency checking by hardware logic at run time is removed and delegated to the compiler. Explicitly parallel instruction computing (EPIC) is like VLIW with extra cache prefetching instructions.

Simultaneous multithreading (SMT) is a technique for improving the overall efficiency of superscalar processors. SMT permits multiple independent threads of execution to better utilize the resources provided by modern processor architectures.

Superscalar processors differ from multi-core processors in that the several execution units are not entire processors. A single processor is composed of finer-grained execution units such as the ALU, integer multiplier, integer shifter, FPU, etc. There may be multiple versions of each execution unit to enable execution of many instructions in parallel. This differs from a multi-core processor that concurrently processes instructions from multiple threads, one thread per processing unit (called «core»). It also differs from a pipelined processor, where the multiple instructions can concurrently be in various stages of execution, assembly-line fashion.

The various alternative techniques are not mutually exclusive—they can be (and frequently are) combined in a single processor. Thus a multicore CPU is possible where each core is an independent processor containing multiple parallel pipelines, each pipeline being superscalar. Some processors also include vector capability.

See also[edit]

- Eager execution

- Hyper-threading

- Simultaneous multithreading

- Out-of-order execution

- Shelving buffer

- Speculative execution

- Software lockout, a multiprocessor issue similar to logic dependencies on superscalars

- Super-threading

References[edit]

- ^ «What is a Superscalar Processor? — Definition from Techopedia». Techopedia.com. Retrieved 2022-08-29.

- Mike Johnson, Superscalar Microprocessor Design, Prentice-Hall, 1991, ISBN 0-13-875634-1

- Sorin Cotofana, Stamatis Vassiliadis, «On the Design Complexity of the Issue Logic of Superscalar Machines», EUROMICRO 1998: 10277-10284

- Steven McGeady, «The i960CA SuperScalar Implementation of the 80960 Architecture», IEEE 1990, pp. 232–240

- Steven McGeady, et al., «Performance Enhancements in the Superscalar i960MM Embedded Microprocessor,» ACM Proceedings of the 1991 Conference on Computer Architecture (Compcon), 1991, pp. 4–7

External links[edit]

- Eager Execution / Dual Path / Multiple Path, By Mark Smotherman

Суперскалярность

-

Суперскалярный процессор (англ. superscalar processor) — процессор, поддерживающий так называемый параллелизм на уровне инструкций (то есть, процессор, способный выполнять несколько инструкций одновременно) за счёт включения в состав его вычислительного ядра нескольких одинаковых функциональных узлов (таких как АЛУ, FPU, умножитель (integer multiplier), сдвигающее устройство (integer shifter) и другие устройства). Планирование исполнения потока инструкций осуществляется динамически вычислительным ядром (не статически компилятором).

Способы увеличения производительности, которые могут использоваться совместно:

Использование конвейера (англ. pipelining)

* увеличение количества функциональных узлов процессора (суперскалярность)

* увеличение количества ядер (многоядерность)

увеличение количества процессоров (многопроцессорность)При использовании конвейера количество узлов остаётся прежним; увеличение производительности достигается за счёт одновременной работы узлов, ответственных за разные стадии обработки инструкций одного потока. При использовании суперскалярности увеличение производительности достигается за счёт одновременной работы большего количества одинаковых узлов, независимо обрабатывающих инструкции одного потока (в том числе, и большего количества конвейеров). При использовании нескольких ядер каждое ядро выполняет инструкции отдельного потока, причем каждое из них может быть суперскалярным и/или конвейерным. При использовании нескольких процессоров каждый процессор может быть многоядерным.

В суперскалярном процессоре инструкция извлекается из потока инструкций (находящегося в памяти), определяется наличие или отсутствие зависимости инструкции по данным от других инструкций, затем инструкция выполняется. Одновременно, в течение одного такта, может выполняться несколько независимых инструкций.

По классификации Флинна одноядерные суперскалярные процессоры относят к группе процессоров SISD (англ. single instruction stream, single data stream — один поток инструкций, один поток данных). Подобные процессоры, поддерживающие инструкции для работы с короткими векторами, могут быть отнесены к группе SIMD (англ. single instruction stream, multiple data streams — один поток инструкций, несколько потоков данных). Многоядерные суперскалярные процессоры относят к группе MIMD (англ. multiple instruction streams, multiple data streams — несколько потоков инструкций, несколько потоков данных).

Источник: Википедия

Связанные понятия

Внеочередное исполнение (англ. out-of-order execution) машинных инструкций — исполнение машинных инструкций не в порядке следования в машинном коде (как было при выполнении инструкций по порядку (англ. in-order execution)), а в порядке готовности к выполнению. Реализуется с целью повышения производительности вычислительных устройств. Среди широко известных машин впервые в существенной мере реализована в машинах CDC 6600 компании Control Data и IBM System/360 Model 91 компании IBM.

Архитектура набора команд (англ. instruction set architecture, ISA) — часть архитектуры компьютера, определяющая программируемую часть ядра микропроцессора. На этом уровне определяются реализованные в микропроцессоре конкретного типа…

Термин «ядро микропроцессора» (англ. processor core) не имеет чёткого определения и в зависимости от контекста употребления может обозначать особенности, позволяющие выделить модель в отдельный вид…

Систе́ма кома́нд (также набо́р команд) — соглашение о предоставляемых архитектурой средствах программирования, а именно…

Конве́йер — способ организации вычислений, используемый в современных процессорах и контроллерах с целью повышения их производительности (увеличения числа инструкций, выполняемых в единицу времени — эксплуатация параллелизма на уровне инструкций), технология, используемая при разработке компьютеров и других цифровых электронных устройств.

Математический сопроцессор — сопроцессор для расширения командного множества центрального процессора и обеспечивающий его функциональностью модуля операций с плавающей запятой, для процессоров, не имеющих интегрированного модуля.

Микроко́д — программа, реализующая набор инструкций процессора. Так же как одна инструкция языка высокого уровня преобразуется в серию машинных инструкций, в процессоре, использующем микрокод, каждая машинная инструкция реализуется в виде серии микроинструкций — микропрограммы, микрокода.

Архитекту́ра проце́ссора — количественная составляющая компонентов микроархитектуры вычислительной машины (процессора компьютера) (например, регистр флагов или регистры процессора), рассматриваемая IT-специалистами в аспекте прикладной деятельности.

В компьютерной инженерии микроархитектура (англ. microarchitecture; иногда сокращается до µarch или uarch), также называемая организация компьютера — это способ, которым данная архитектура набора команд (ISA, АНК) реализована в процессоре. Каждая АНК может быть реализована с помощью различных микроархитектур.

Сопроцессор — специализированный процессор, расширяющий возможности центрального процессора компьютерной системы, но оформленный как отдельный функциональный модуль. Физически сопроцессор может быть отдельной микросхемой или может быть встроен в центральный процессор (как это делается в случае математического сопроцессора в процессорах для ПК начиная с Intel 486DX).

Параллелизм на уровне команд (англ. Instruction-level parallelism — ILP) является мерой того, какое множество операций в компьютерной программе может выполняться одновременно. Потенциальное совмещение выполнения команд называется «параллелизмом на уровне команд».

Многопроцессорностью иногда называют выполнение множественных параллельных программных процессов в системе в противоположность выполнению одного процесса в любой момент времени. Однако термины многозадачность или мультипрограммирование являются более подходящими для описания этого понятия, которое осуществлено главным образом в программном обеспечении, тогда как многопроцессорная обработка является более соответствующей, чтобы описать использование множественных аппаратных процессоров. Система не…

Центра́льный проце́ссор (ЦП; также центра́льное проце́ссорное устро́йство — ЦПУ; англ. central processing unit, CPU, дословно — центральное обрабатывающее устройство) — электронный блок либо интегральная схема (микропроцессор), исполняющая машинные инструкции (код программ), главная часть аппаратного обеспечения компьютера или программируемого логического контроллера. Иногда называют микропроцессором или просто процессором.

Контроллер памяти — цифровая схема, управляющая потоками данных между вычислительной системой и оперативной памятью. Может представлять собой отдельную микросхему или быть интегрирована в более сложную микросхему, например, в состав северного моста, микропроцессор или систему на кристалле.

Блок управления памятью или устройство управления памятью (англ. memory management unit, MMU) — компонент аппаратного обеспечения компьютера, отвечающий за управление доступом к памяти, запрашиваемым центральным процессором.

Северный мост (англ. north bridge) — контроллер (чип), являющийся одним из элементов чипсета материнской (системной) платы и отвечающий за работу центрального процессора (CPU) с ОЗУ (оперативной памятью, RAM) и видеоадаптером.

Мультипроцессор (от англ. multiprocessor, multiprocessing) — это подкласс многопроцессорных компьютерных систем, где есть несколько процессоров и одно адресное пространство, видимое для всех процессоров. В таксономии Флинна мультипроцессоры относятся к классу SM-MIMD-машин. Мультипроцессор запускает одну копию ОС с одним набором таблиц, в том числе тех, которые следят какие страницы памяти свободны.

Многоя́дерный проце́ссор — центральный процессор, содержащий два и более вычислительных ядра на одном процессорном кристалле или в одном корпусе.

Векторный процессор — это процессор, в котором операндами некоторых команд могут выступать упорядоченные массивы данных — векторы. Отличается от скалярных процессоров, которые могут работать только с одним операндом в единицу времени. Абсолютное большинство процессоров является скалярными или близкими к ним. Векторные процессоры были распространены в сфере научных вычислений, где они являлись основой большинства суперкомпьютеров начиная с 1980-х до 1990-х. Но резкое увеличение производительности…

Защищённый режим (режим защищённой виртуальной адресации) — режим работы x86-совместимых процессоров. Частично был реализован уже в процессоре 80286, но там существенно отличался способ работы с памятью, так как процессоры ещё были 16-битными и не была реализована страничная организация памяти. Первая 32-битная реализация защищённого режима — процессор Intel 80386. Применяется в совместимых процессорах других производителей. Данный режим используется в современных многозадачных операционных системах…

Программи́руемая логи́ческая интегра́льная схе́ма (ПЛИС, англ. programmable logic device, PLD) — электронный компонент (интегральная микросхема), используемый для создания конфигурируемых цифровых электронных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования). Для программирования используются программатор и IDE (отладочная среда), позволяющие задать желаемую структуру цифрового устройства в…

Подробнее: ПЛИС

Одновременная многопоточность (англ. Simultaneous Multithreading — SMT) — одна из двух главных форм многопоточности, которая может быть реализована в процессорах аппаратно. Второй формой является временная многопоточность. Технология одновременной многопоточности позволяет исполнять инструкции из нескольких независимых потоков выполнения на множестве функциональных модулей суперскалярного микропроцессора в одном цикле.

Шина адреса — компьютерная шина, используемая центральным процессором или устройствами, способными инициировать сеансы DMA, для указания физического адреса слова ОЗУ (или начала блока слов), к которому устройство может обратиться для проведения операции чтения или записи.

Южный мост (англ. Southbridge) — функциональный контроллер, также известен как контроллер-концентратор ввода-вывода (от англ. I/O Controller Hub, ICH).

Счётчик кома́нд (также PC = program counter, IP = instruction pointer, IAR = instruction address register, СЧАК = счётчик адресуемых команд) — регистр процессора, который указывает, какую команду нужно выполнять следующей.

Кэш микропроцессора — кэш (сверхоперативная память), используемый микропроцессором компьютера для уменьшения среднего времени доступа к компьютерной памяти. Является одним из верхних уровней иерархии памяти. Кэш использует небольшую, очень быструю память (обычно типа SRAM), которая хранит копии часто используемых данных из основной памяти. Если большая часть запросов в память будет обрабатываться кэшем, средняя задержка обращения к памяти будет приближаться к задержкам работы кэша.

Реальный режим (или режим реальных адресов; англ. real-address mode) — режим работы процессоров архитектуры x86, при котором используется сегментная адресация памяти (адрес ячейки памяти формируется из двух чисел: сдвинутого на 4 бита адреса начала сегмента и смещения ячейки от начала сегмента; любому процессу доступна вся память компьютера). Изначально режим не имел названия, был назван «реальным» только после создания процессоров 80286, поддерживающих режим, названный «защищённым» (режим назван…

Графический процессор (англ. graphics processing unit, GPU) — отдельное устройство персонального компьютера или игровой приставки, выполняющее графический рендеринг; в начале 2000-х годов графические процессоры стали массово применяться и в других устройствах: планшетные компьютеры, встраиваемые системы, цифровые телевизоры.

AMP или ASMP (от англ.: Asymmetric multiprocessing, рус.: Асимметричная многопроцессорная обработка или Асимметричное мультипроцессирование) — тип многопроцессорной обработки, который использовался до того, как была создана технология симметричного мультипроцессирования (SMP); также использовался как более дешевая альтернатива в системах, которые поддерживали SMP.

Подробнее: Асимметричное мультипроцессирование

Прямой доступ к памяти (англ. direct memory access, DMA) — режим обмена данными между устройствами компьютера или же между устройством и основной памятью, в котором центральный процессор (ЦП) не участвует. Так как данные не пересылаются в ЦП и обратно, скорость передачи увеличивается.

Операти́вная па́мять (англ. Random Access Memory, RAM, память с произвольным доступом) или операти́вное запомина́ющее устро́йство (ОЗУ) — энергозависимая часть системы компьютерной памяти, в которой во время работы компьютера хранится выполняемый машинный код (программы), а также входные, выходные и промежуточные данные, обрабатываемые процессором.

Массово-параллельная архитектура (англ. massive parallel processing, MPP, также «массивно-параллельная архитектура») — класс архитектур параллельных вычислительных систем. Особенность архитектуры состоит в том, что память физически разделена.

Прерывание (англ. interrupt) — сигнал от программного или аппаратного обеспечения, сообщающий процессору о наступлении какого-либо события, требующего немедленного внимания. Прерывание извещает процессор о наступлении высокоприоритетного события, требующего прерывания текущего кода, выполняемого процессором. Процессор отвечает приостановкой своей текущей активности, сохраняя свое состояние и выполняя функцию, называемую обработчиком прерывания (или программой обработки прерывания), которая реагирует…

Вычислительная мощность компьютера (производительность компьютера) — это количественная характеристика скорости выполнения определённых операций на компьютере. Чаще всего вычислительная мощность измеряется во флопсах (количество операций с плавающей запятой в секунду), а также производными от неё. На данный момент принято причислять к суперкомпьютерам системы с вычислительной мощностью более 10 терафлопсов (10*1012 или десять триллионов флопсов; для сравнения — среднестатистический современный настольный…

Систе́ма на криста́лле (СнК), однокриста́льная систе́ма (англ. System-on-a-Chip, SoC (произносится как «эс-оу-си»)) — в микроэлектронике — электронная схема, выполняющая функции целого устройства (например, компьютера) и размещённая на одной интегральной схеме.

Аппаратная виртуализация — виртуализация с поддержкой специальной процессорной архитектуры. В отличие от программной виртуализации, с помощью данной техники возможно использование изолированных гостевых систем, управляемых гипервизором напрямую.

Компьютерная ши́на (англ. computer bus) в архитектуре компьютера — подсистема, служащая для передачи данных между функциональными блоками компьютера. В устройстве шины можно различить механический, электрический (физический) и логический (управляющий) уровни.

Подробнее: Шина (компьютер)

Цифровой сигнальный процессор (англ. digital signal processor, DSP, цифровой процессор обработки сигналов (ЦПОС)) — специализированный микропроцессор, предназначенный для обработки оцифрованных сигналов (обычно, в режиме реального времени).

Программи́руемая по́льзователем ве́нтильная ма́трица (ППВМ, англ. field-programmable gate array, FPGA) — полупроводниковое устройство, которое может быть сконфигурировано производителем или разработчиком после изготовления; отсюда название: «программируемая пользователем». ППВМ программируются путём изменения логики работы принципиальной схемы, например, с помощью исходного кода на языке проектирования (типа VHDL), на котором можно описать эту логику работы микросхемы. ППВМ является одной из архитектурных…

Регистр процессора — блок ячеек памяти, образующий сверхбыструю оперативную память (СОЗУ) внутри процессора; используется самим процессором и большей частью недоступен программисту: например, при выборке из памяти очередной команды она помещается в регистр команд, к которому программист обратиться не может.

Встра́иваемая систе́ма (встро́енная систе́ма, англ. embedded system) — специализированная микропроцессорная система управления, контроля и мониторинга, концепция разработки которой заключается в том, что такая система будет работать, будучи встроенной непосредственно в устройство, которым она управляет.

Шина данных — часть системной шины, предназначенная для передачи данных между компонентами компьютера.

Архитекту́ра компью́тера — набор типов данных, операций и характеристик каждого отдельно взятого уровня. Архитектура связана с программными аспектами. Аспекты реализации (например, технология, применяемая при реализации памяти) не являются частью архитектуры.

Когерентность кэша (англ. cache coherence) — свойство кэшей, означающее целостность данных, хранящихся в локальных кэшах для разделяемого ресурса. Когерентность кэшей — частный случай когерентности памяти.

Тактовый сигнал или синхросигнал — сигнал, использующийся для согласования операций одной или более цифровых схем.

Микропроце́ссор — процессор (устройство, отвечающее за выполнение арифметических, логических операций и операций управления, записанных в машинном коде), реализованный в виде одной микросхемы или комплекта из нескольких специализированных микросхем (в отличие от реализации процессора в виде электрической схемы на элементной базе общего назначения или в виде программной модели). Первые микропроцессоры появились в 1970-х годах и применялись в электронных калькуляторах, в них использовалась двоично-десятичная…

Модуль предсказания переходов (прогнозирования ветвлений) (англ. branch prediction unit) — устройство, входящее в состав микропроцессоров, имеющих конвейерную архитектуру, предсказывающее, будет ли выполнен условный переход в исполняемой программе. Предсказание ветвлений позволяет сократить время простоя конвейера за счёт предварительной загрузки и исполнения инструкций, которые должны выполниться после выполнения инструкции условного перехода. Прогнозирование ветвлений играет критическую роль, так…

Сегментная адресация памяти — схема логической адресации памяти компьютера в архитектуре x86. Линейный адрес конкретной ячейки памяти, который в некоторых режимах работы процессора будет совпадать с физическим адресом, делится на две части: сегмент и смещение. Сегментом называется условно выделенная область адресного пространства определённого размера, а смещением — адрес ячейки памяти относительно начала сегмента. Базой сегмента называется линейный адрес (адрес относительно всего объёма памяти…

Суперскалярность

-

Суперскалярный процессор (англ. superscalar processor) — процессор, поддерживающий так называемый параллелизм на уровне инструкций (то есть, процессор, способный выполнять несколько инструкций одновременно) за счёт включения в состав его вычислительного ядра нескольких одинаковых функциональных узлов (таких как АЛУ, FPU, умножитель (integer multiplier), сдвигающее устройство (integer shifter) и другие устройства). Планирование исполнения потока инструкций осуществляется динамически вычислительным ядром (не статически компилятором).

Способы увеличения производительности, которые могут использоваться совместно:

Использование конвейера (англ. pipelining)

* увеличение количества функциональных узлов процессора (суперскалярность)

* увеличение количества ядер (многоядерность)

увеличение количества процессоров (многопроцессорность)При использовании конвейера количество узлов остаётся прежним; увеличение производительности достигается за счёт одновременной работы узлов, ответственных за разные стадии обработки инструкций одного потока. При использовании суперскалярности увеличение производительности достигается за счёт одновременной работы большего количества одинаковых узлов, независимо обрабатывающих инструкции одного потока (в том числе, и большего количества конвейеров). При использовании нескольких ядер каждое ядро выполняет инструкции отдельного потока, причем каждое из них может быть суперскалярным и/или конвейерным. При использовании нескольких процессоров каждый процессор может быть многоядерным.

В суперскалярном процессоре инструкция извлекается из потока инструкций (находящегося в памяти), определяется наличие или отсутствие зависимости инструкции по данным от других инструкций, затем инструкция выполняется. Одновременно, в течение одного такта, может выполняться несколько независимых инструкций.

По классификации Флинна одноядерные суперскалярные процессоры относят к группе процессоров SISD (англ. single instruction stream, single data stream — один поток инструкций, один поток данных). Подобные процессоры, поддерживающие инструкции для работы с короткими векторами, могут быть отнесены к группе SIMD (англ. single instruction stream, multiple data streams — один поток инструкций, несколько потоков данных). Многоядерные суперскалярные процессоры относят к группе MIMD (англ. multiple instruction streams, multiple data streams — несколько потоков инструкций, несколько потоков данных).

Источник: Википедия

Связанные понятия

Внеочередное исполнение (англ. out-of-order execution) машинных инструкций — исполнение машинных инструкций не в порядке следования в машинном коде (как было при выполнении инструкций по порядку (англ. in-order execution)), а в порядке готовности к выполнению. Реализуется с целью повышения производительности вычислительных устройств. Среди широко известных машин впервые в существенной мере реализована в машинах CDC 6600 компании Control Data и IBM System/360 Model 91 компании IBM.

Архитектура набора команд (англ. instruction set architecture, ISA) — часть архитектуры компьютера, определяющая программируемую часть ядра микропроцессора. На этом уровне определяются реализованные в микропроцессоре конкретного типа…

Термин «ядро микропроцессора» (англ. processor core) не имеет чёткого определения и в зависимости от контекста употребления может обозначать особенности, позволяющие выделить модель в отдельный вид…

Систе́ма кома́нд (также набо́р команд) — соглашение о предоставляемых архитектурой средствах программирования, а именно…

Конве́йер — способ организации вычислений, используемый в современных процессорах и контроллерах с целью повышения их производительности (увеличения числа инструкций, выполняемых в единицу времени — эксплуатация параллелизма на уровне инструкций), технология, используемая при разработке компьютеров и других цифровых электронных устройств.

Математический сопроцессор — сопроцессор для расширения командного множества центрального процессора и обеспечивающий его функциональностью модуля операций с плавающей запятой, для процессоров, не имеющих интегрированного модуля.

Микроко́д — программа, реализующая набор инструкций процессора. Так же как одна инструкция языка высокого уровня преобразуется в серию машинных инструкций, в процессоре, использующем микрокод, каждая машинная инструкция реализуется в виде серии микроинструкций — микропрограммы, микрокода.

Архитекту́ра проце́ссора — количественная составляющая компонентов микроархитектуры вычислительной машины (процессора компьютера) (например, регистр флагов или регистры процессора), рассматриваемая IT-специалистами в аспекте прикладной деятельности.

В компьютерной инженерии микроархитектура (англ. microarchitecture; иногда сокращается до µarch или uarch), также называемая организация компьютера — это способ, которым данная архитектура набора команд (ISA, АНК) реализована в процессоре. Каждая АНК может быть реализована с помощью различных микроархитектур.

Сопроцессор — специализированный процессор, расширяющий возможности центрального процессора компьютерной системы, но оформленный как отдельный функциональный модуль. Физически сопроцессор может быть отдельной микросхемой или может быть встроен в центральный процессор (как это делается в случае математического сопроцессора в процессорах для ПК начиная с Intel 486DX).

Параллелизм на уровне команд (англ. Instruction-level parallelism — ILP) является мерой того, какое множество операций в компьютерной программе может выполняться одновременно. Потенциальное совмещение выполнения команд называется «параллелизмом на уровне команд».

Многопроцессорностью иногда называют выполнение множественных параллельных программных процессов в системе в противоположность выполнению одного процесса в любой момент времени. Однако термины многозадачность или мультипрограммирование являются более подходящими для описания этого понятия, которое осуществлено главным образом в программном обеспечении, тогда как многопроцессорная обработка является более соответствующей, чтобы описать использование множественных аппаратных процессоров. Система не…

Центра́льный проце́ссор (ЦП; также центра́льное проце́ссорное устро́йство — ЦПУ; англ. central processing unit, CPU, дословно — центральное обрабатывающее устройство) — электронный блок либо интегральная схема (микропроцессор), исполняющая машинные инструкции (код программ), главная часть аппаратного обеспечения компьютера или программируемого логического контроллера. Иногда называют микропроцессором или просто процессором.

Контроллер памяти — цифровая схема, управляющая потоками данных между вычислительной системой и оперативной памятью. Может представлять собой отдельную микросхему или быть интегрирована в более сложную микросхему, например, в состав северного моста, микропроцессор или систему на кристалле.

Блок управления памятью или устройство управления памятью (англ. memory management unit, MMU) — компонент аппаратного обеспечения компьютера, отвечающий за управление доступом к памяти, запрашиваемым центральным процессором.

Северный мост (англ. north bridge) — контроллер (чип), являющийся одним из элементов чипсета материнской (системной) платы и отвечающий за работу центрального процессора (CPU) с ОЗУ (оперативной памятью, RAM) и видеоадаптером.

Мультипроцессор (от англ. multiprocessor, multiprocessing) — это подкласс многопроцессорных компьютерных систем, где есть несколько процессоров и одно адресное пространство, видимое для всех процессоров. В таксономии Флинна мультипроцессоры относятся к классу SM-MIMD-машин. Мультипроцессор запускает одну копию ОС с одним набором таблиц, в том числе тех, которые следят какие страницы памяти свободны.

Многоя́дерный проце́ссор — центральный процессор, содержащий два и более вычислительных ядра на одном процессорном кристалле или в одном корпусе.

Векторный процессор — это процессор, в котором операндами некоторых команд могут выступать упорядоченные массивы данных — векторы. Отличается от скалярных процессоров, которые могут работать только с одним операндом в единицу времени. Абсолютное большинство процессоров является скалярными или близкими к ним. Векторные процессоры были распространены в сфере научных вычислений, где они являлись основой большинства суперкомпьютеров начиная с 1980-х до 1990-х. Но резкое увеличение производительности…

Защищённый режим (режим защищённой виртуальной адресации) — режим работы x86-совместимых процессоров. Частично был реализован уже в процессоре 80286, но там существенно отличался способ работы с памятью, так как процессоры ещё были 16-битными и не была реализована страничная организация памяти. Первая 32-битная реализация защищённого режима — процессор Intel 80386. Применяется в совместимых процессорах других производителей. Данный режим используется в современных многозадачных операционных системах…

Программи́руемая логи́ческая интегра́льная схе́ма (ПЛИС, англ. programmable logic device, PLD) — электронный компонент (интегральная микросхема), используемый для создания конфигурируемых цифровых электронных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования). Для программирования используются программатор и IDE (отладочная среда), позволяющие задать желаемую структуру цифрового устройства в…

Подробнее: ПЛИС

Одновременная многопоточность (англ. Simultaneous Multithreading — SMT) — одна из двух главных форм многопоточности, которая может быть реализована в процессорах аппаратно. Второй формой является временная многопоточность. Технология одновременной многопоточности позволяет исполнять инструкции из нескольких независимых потоков выполнения на множестве функциональных модулей суперскалярного микропроцессора в одном цикле.

Шина адреса — компьютерная шина, используемая центральным процессором или устройствами, способными инициировать сеансы DMA, для указания физического адреса слова ОЗУ (или начала блока слов), к которому устройство может обратиться для проведения операции чтения или записи.

Южный мост (англ. Southbridge) — функциональный контроллер, также известен как контроллер-концентратор ввода-вывода (от англ. I/O Controller Hub, ICH).

Счётчик кома́нд (также PC = program counter, IP = instruction pointer, IAR = instruction address register, СЧАК = счётчик адресуемых команд) — регистр процессора, который указывает, какую команду нужно выполнять следующей.

Кэш микропроцессора — кэш (сверхоперативная память), используемый микропроцессором компьютера для уменьшения среднего времени доступа к компьютерной памяти. Является одним из верхних уровней иерархии памяти. Кэш использует небольшую, очень быструю память (обычно типа SRAM), которая хранит копии часто используемых данных из основной памяти. Если большая часть запросов в память будет обрабатываться кэшем, средняя задержка обращения к памяти будет приближаться к задержкам работы кэша.

Реальный режим (или режим реальных адресов; англ. real-address mode) — режим работы процессоров архитектуры x86, при котором используется сегментная адресация памяти (адрес ячейки памяти формируется из двух чисел: сдвинутого на 4 бита адреса начала сегмента и смещения ячейки от начала сегмента; любому процессу доступна вся память компьютера). Изначально режим не имел названия, был назван «реальным» только после создания процессоров 80286, поддерживающих режим, названный «защищённым» (режим назван…

Графический процессор (англ. graphics processing unit, GPU) — отдельное устройство персонального компьютера или игровой приставки, выполняющее графический рендеринг; в начале 2000-х годов графические процессоры стали массово применяться и в других устройствах: планшетные компьютеры, встраиваемые системы, цифровые телевизоры.

AMP или ASMP (от англ.: Asymmetric multiprocessing, рус.: Асимметричная многопроцессорная обработка или Асимметричное мультипроцессирование) — тип многопроцессорной обработки, который использовался до того, как была создана технология симметричного мультипроцессирования (SMP); также использовался как более дешевая альтернатива в системах, которые поддерживали SMP.

Подробнее: Асимметричное мультипроцессирование

Прямой доступ к памяти (англ. direct memory access, DMA) — режим обмена данными между устройствами компьютера или же между устройством и основной памятью, в котором центральный процессор (ЦП) не участвует. Так как данные не пересылаются в ЦП и обратно, скорость передачи увеличивается.

Операти́вная па́мять (англ. Random Access Memory, RAM, память с произвольным доступом) или операти́вное запомина́ющее устро́йство (ОЗУ) — энергозависимая часть системы компьютерной памяти, в которой во время работы компьютера хранится выполняемый машинный код (программы), а также входные, выходные и промежуточные данные, обрабатываемые процессором.

Массово-параллельная архитектура (англ. massive parallel processing, MPP, также «массивно-параллельная архитектура») — класс архитектур параллельных вычислительных систем. Особенность архитектуры состоит в том, что память физически разделена.

Прерывание (англ. interrupt) — сигнал от программного или аппаратного обеспечения, сообщающий процессору о наступлении какого-либо события, требующего немедленного внимания. Прерывание извещает процессор о наступлении высокоприоритетного события, требующего прерывания текущего кода, выполняемого процессором. Процессор отвечает приостановкой своей текущей активности, сохраняя свое состояние и выполняя функцию, называемую обработчиком прерывания (или программой обработки прерывания), которая реагирует…

Вычислительная мощность компьютера (производительность компьютера) — это количественная характеристика скорости выполнения определённых операций на компьютере. Чаще всего вычислительная мощность измеряется во флопсах (количество операций с плавающей запятой в секунду), а также производными от неё. На данный момент принято причислять к суперкомпьютерам системы с вычислительной мощностью более 10 терафлопсов (10*1012 или десять триллионов флопсов; для сравнения — среднестатистический современный настольный…

Систе́ма на криста́лле (СнК), однокриста́льная систе́ма (англ. System-on-a-Chip, SoC (произносится как «эс-оу-си»)) — в микроэлектронике — электронная схема, выполняющая функции целого устройства (например, компьютера) и размещённая на одной интегральной схеме.

Аппаратная виртуализация — виртуализация с поддержкой специальной процессорной архитектуры. В отличие от программной виртуализации, с помощью данной техники возможно использование изолированных гостевых систем, управляемых гипервизором напрямую.

Компьютерная ши́на (англ. computer bus) в архитектуре компьютера — подсистема, служащая для передачи данных между функциональными блоками компьютера. В устройстве шины можно различить механический, электрический (физический) и логический (управляющий) уровни.

Подробнее: Шина (компьютер)

Цифровой сигнальный процессор (англ. digital signal processor, DSP, цифровой процессор обработки сигналов (ЦПОС)) — специализированный микропроцессор, предназначенный для обработки оцифрованных сигналов (обычно, в режиме реального времени).

Программи́руемая по́льзователем ве́нтильная ма́трица (ППВМ, англ. field-programmable gate array, FPGA) — полупроводниковое устройство, которое может быть сконфигурировано производителем или разработчиком после изготовления; отсюда название: «программируемая пользователем». ППВМ программируются путём изменения логики работы принципиальной схемы, например, с помощью исходного кода на языке проектирования (типа VHDL), на котором можно описать эту логику работы микросхемы. ППВМ является одной из архитектурных…

Регистр процессора — блок ячеек памяти, образующий сверхбыструю оперативную память (СОЗУ) внутри процессора; используется самим процессором и большей частью недоступен программисту: например, при выборке из памяти очередной команды она помещается в регистр команд, к которому программист обратиться не может.

Встра́иваемая систе́ма (встро́енная систе́ма, англ. embedded system) — специализированная микропроцессорная система управления, контроля и мониторинга, концепция разработки которой заключается в том, что такая система будет работать, будучи встроенной непосредственно в устройство, которым она управляет.

Шина данных — часть системной шины, предназначенная для передачи данных между компонентами компьютера.

Архитекту́ра компью́тера — набор типов данных, операций и характеристик каждого отдельно взятого уровня. Архитектура связана с программными аспектами. Аспекты реализации (например, технология, применяемая при реализации памяти) не являются частью архитектуры.

Когерентность кэша (англ. cache coherence) — свойство кэшей, означающее целостность данных, хранящихся в локальных кэшах для разделяемого ресурса. Когерентность кэшей — частный случай когерентности памяти.

Тактовый сигнал или синхросигнал — сигнал, использующийся для согласования операций одной или более цифровых схем.

Микропроце́ссор — процессор (устройство, отвечающее за выполнение арифметических, логических операций и операций управления, записанных в машинном коде), реализованный в виде одной микросхемы или комплекта из нескольких специализированных микросхем (в отличие от реализации процессора в виде электрической схемы на элементной базе общего назначения или в виде программной модели). Первые микропроцессоры появились в 1970-х годах и применялись в электронных калькуляторах, в них использовалась двоично-десятичная…

Модуль предсказания переходов (прогнозирования ветвлений) (англ. branch prediction unit) — устройство, входящее в состав микропроцессоров, имеющих конвейерную архитектуру, предсказывающее, будет ли выполнен условный переход в исполняемой программе. Предсказание ветвлений позволяет сократить время простоя конвейера за счёт предварительной загрузки и исполнения инструкций, которые должны выполниться после выполнения инструкции условного перехода. Прогнозирование ветвлений играет критическую роль, так…

Сегментная адресация памяти — схема логической адресации памяти компьютера в архитектуре x86. Линейный адрес конкретной ячейки памяти, который в некоторых режимах работы процессора будет совпадать с физическим адресом, делится на две части: сегмент и смещение. Сегментом называется условно выделенная область адресного пространства определённого размера, а смещением — адрес ячейки памяти относительно начала сегмента. Базой сегмента называется линейный адрес (адрес относительно всего объёма памяти…

From Wikipedia, the free encyclopedia

«Superscaler» redirects here. For the Sega arcade system board, see Sega Super Scaler.

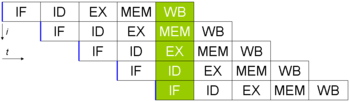

Simple superscalar pipeline. By fetching and dispatching two instructions at a time, a maximum of two instructions per cycle can be completed. (IF = instruction fetch, ID = instruction decode, EX = execute, MEM = memory access, WB = register write-back, i = instruction number, t = clock cycle [i.e. time])

A superscalar processor is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor.[1] In contrast to a scalar processor, which can execute at most one single instruction per clock cycle, a superscalar processor can execute more than one instruction during a clock cycle by simultaneously dispatching multiple instructions to different execution units on the processor. It therefore allows more throughput (the number of instructions that can be executed in a unit of time) than would otherwise be possible at a given clock rate. Each execution unit is not a separate processor (or a core if the processor is a multi-core processor), but an execution resource within a single CPU such as an arithmetic logic unit.

In Flynn’s taxonomy, a single-core superscalar processor is classified as an SISD processor (single instruction stream, single data stream), though a single-core superscalar processor that supports short vector operations could be classified as SIMD (single instruction stream, multiple data streams). A multi-core superscalar processor is classified as an MIMD processor (multiple instruction streams, multiple data streams).

While a superscalar CPU is typically also pipelined, superscalar and pipelining execution are considered different performance enhancement techniques. The former executes multiple instructions in parallel by using multiple execution units, whereas the latter executes multiple instructions in the same execution unit in parallel by dividing the execution unit into different phases.

The superscalar technique is traditionally associated with several identifying characteristics (within a given CPU):

- Instructions are issued from a sequential instruction stream

- The CPU dynamically checks for data dependencies between instructions at run time (versus software checking at compile time)

- The CPU can execute multiple instructions per clock cycle

History[edit]

Seymour Cray’s CDC 6600 from 1964 is often mentioned as the first superscalar design. The 1967 IBM System/360 Model 91 was another superscalar mainframe. The Motorola MC88100 (1988), the Intel i960CA (1989) and the AMD 29000-series 29050 (1990) microprocessors were the first commercial single-chip superscalar microprocessors. RISC microprocessors like these were the first to have superscalar execution, because RISC architectures free transistors and die area which can be used to include multiple execution units (this was why RISC designs were faster than CISC designs through the 1980s and into the 1990s).

Except for CPUs used in low-power applications, embedded systems, and battery-powered devices, essentially all general-purpose CPUs developed since about 1998 are superscalar.

The P5 Pentium was the first superscalar x86 processor; the Nx586, P6 Pentium Pro and AMD K5 were among the first designs which decode x86-instructions asynchronously into dynamic microcode-like micro-op sequences prior to actual execution on a superscalar microarchitecture; this opened up for dynamic scheduling of buffered partial instructions and enabled more parallelism to be extracted compared to the more rigid methods used in the simpler P5 Pentium; it also simplified speculative execution and allowed higher clock frequencies compared to designs such as the advanced Cyrix 6×86.

Scalar to superscalar[edit]

The simplest processors are scalar processors. Each instruction executed by a scalar processor typically manipulates one or two data items at a time. By contrast, each instruction executed by a vector processor operates simultaneously on many data items. An analogy is the difference between scalar and vector arithmetic. A superscalar processor is a mixture of the two. Each instruction processes one data item, but there are multiple execution units within each CPU thus multiple instructions can be processing separate data items concurrently.

Superscalar CPU design emphasizes improving the instruction dispatcher accuracy, and allowing it to keep the multiple execution units in use at all times. This has become increasingly important as the number of units has increased. While early superscalar CPUs would have two ALUs and a single FPU, a later design such as the PowerPC 970 includes four ALUs, two FPUs, and two SIMD units. If the dispatcher is ineffective at keeping all of these units fed with instructions, the performance of the system will be no better than that of a simpler, cheaper design.

A superscalar processor usually sustains an execution rate in excess of one instruction per machine cycle. But merely processing multiple instructions concurrently does not make an architecture superscalar, since pipelined, multiprocessor or multi-core architectures also achieve that, but with different methods.

In a superscalar CPU the dispatcher reads instructions from memory and decides which ones can be run in parallel, dispatching each to one of the several execution units contained inside a single CPU. Therefore, a superscalar processor can be envisioned having multiple parallel pipelines, each of which is processing instructions simultaneously from a single instruction thread.

Limitations[edit]

Available performance improvement from superscalar techniques is limited by three key areas:

- The degree of intrinsic parallelism in the instruction stream (instructions requiring the same computational resources from the CPU)

- The complexity and time cost of dependency checking logic and register renaming circuitry

- The branch instruction processing

Existing binary executable programs have varying degrees of intrinsic parallelism. In some cases instructions are not dependent on each other and can be executed simultaneously. In other cases they are inter-dependent: one instruction impacts either resources or results of the other. The instructions a = b + c; d = e + f can be run in parallel because none of the results depend on other calculations. However, the instructions a = b + c; b = e + f might not be runnable in parallel, depending on the order in which the instructions complete while they move through the units.

Although the instruction stream may contain no inter-instruction dependencies, a superscalar CPU must nonetheless check for that possibility, since there is no assurance otherwise and failure to detect a dependency would produce incorrect results.

No matter how advanced the semiconductor process or how fast the switching speed, this places a practical limit on how many instructions can be simultaneously dispatched. While process advances will allow ever greater numbers of execution units (e.g. ALUs), the burden of checking instruction dependencies grows rapidly, as does the complexity of register renaming circuitry to mitigate some dependencies. Collectively the power consumption, complexity and gate delay costs limit the achievable superscalar speedup.

However even given infinitely fast dependency checking logic on an otherwise conventional superscalar CPU, if the instruction stream itself has many dependencies, this would also limit the possible speedup. Thus the degree of intrinsic parallelism in the code stream forms a second limitation.

Alternatives[edit]

Collectively, these limits drive investigation into alternative architectural changes such as very long instruction word (VLIW), explicitly parallel instruction computing (EPIC), simultaneous multithreading (SMT), and multi-core computing.

With VLIW, the burdensome task of dependency checking by hardware logic at run time is removed and delegated to the compiler. Explicitly parallel instruction computing (EPIC) is like VLIW with extra cache prefetching instructions.

Simultaneous multithreading (SMT) is a technique for improving the overall efficiency of superscalar processors. SMT permits multiple independent threads of execution to better utilize the resources provided by modern processor architectures.

Superscalar processors differ from multi-core processors in that the several execution units are not entire processors. A single processor is composed of finer-grained execution units such as the ALU, integer multiplier, integer shifter, FPU, etc. There may be multiple versions of each execution unit to enable execution of many instructions in parallel. This differs from a multi-core processor that concurrently processes instructions from multiple threads, one thread per processing unit (called «core»). It also differs from a pipelined processor, where the multiple instructions can concurrently be in various stages of execution, assembly-line fashion.

The various alternative techniques are not mutually exclusive—they can be (and frequently are) combined in a single processor. Thus a multicore CPU is possible where each core is an independent processor containing multiple parallel pipelines, each pipeline being superscalar. Some processors also include vector capability.

See also[edit]

- Eager execution

- Hyper-threading

- Simultaneous multithreading

- Out-of-order execution

- Shelving buffer

- Speculative execution

- Software lockout, a multiprocessor issue similar to logic dependencies on superscalars

- Super-threading

References[edit]

- ^ «What is a Superscalar Processor? — Definition from Techopedia». Techopedia.com. Retrieved 2022-08-29.

- Mike Johnson, Superscalar Microprocessor Design, Prentice-Hall, 1991, ISBN 0-13-875634-1

- Sorin Cotofana, Stamatis Vassiliadis, «On the Design Complexity of the Issue Logic of Superscalar Machines», EUROMICRO 1998: 10277-10284

- Steven McGeady, «The i960CA SuperScalar Implementation of the 80960 Architecture», IEEE 1990, pp. 232–240

- Steven McGeady, et al., «Performance Enhancements in the Superscalar i960MM Embedded Microprocessor,» ACM Proceedings of the 1991 Conference on Computer Architecture (Compcon), 1991, pp. 4–7

External links[edit]

- Eager Execution / Dual Path / Multiple Path, By Mark Smotherman

Суперскалярные процессоры

Поскольку

возможности по совершенствованию

элементной базы уже практически

исчерпаны,

дальнейшее повышение производительности

ВМ лежит в плоскости архитектурных

решении. Как уже отмечалось, одни из

наиболее эффективных подходов в этом

плане — введение в вычислительный

процесс различных уровней параллелизма.

Ранее рассмотренный конвейер команд —

типичный пример такого подхода. Тем же

целям служат и арифметические конвейеры,

где конвейеризации подвергается процесс

выполнения арифметических операций.

Дополнительный уровень параллелизма

реализуется в векторных и матричных

процессорах, но только при обработке

многокомпонентных операндов типа

векторов и массивов. Здесь высокое

быстродействие достигается за счет

одновременной обработки всех компонентов

вектора или массива, однако подобные

операнды характерны лишь для достаточно

узкого круга решаемых задач. Основной

объем вычислительной нагрузки обычно

приходится на скалярные вычисления, то

есть на обработку одиночных операндов,

таких, например, как целые числа. Для

подобных вычислений дополнительный

параллелизм реализуется значительно

сложнее, но тем не менее возможен и

примером могут служить суперскалярные

процессоры.

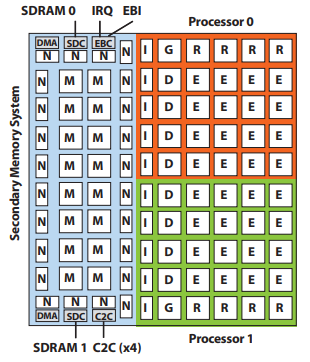

Суперскалярным

(этот

термин впервые был использован в 1987

году [45]) называется центральный процессор

(ЦП), который одновременно выполняет

более чем одну скалярную команду. Это

достигается за счет включения в состав

ЦП нескольких самостоятельных

функциональных (исполнительных) блоков,

каждый из которых отвечает за свой класс

операций и может присутствовать в

процессоре в нескольких экземплярах.

Так, в микропроцессоре Pentium

III

блоки целочисленной арифметики и

операций с плавающей точкой дублированы,

а в микропроцессорах Pentium

4 и Athlon

— троированы. Структура типичного

суперскалярного процессора [234] показана

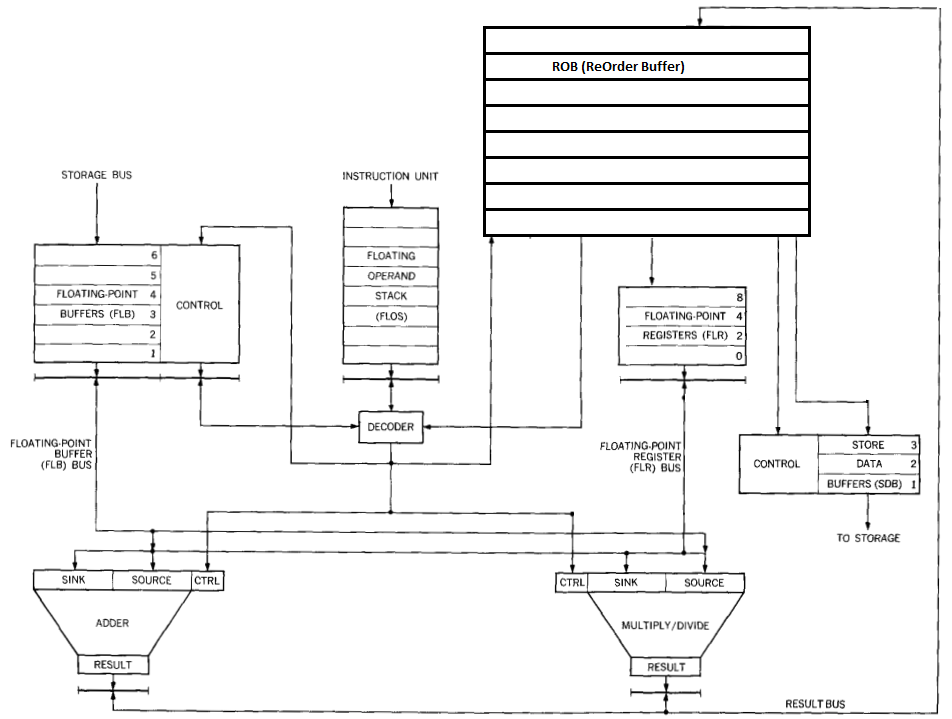

на рис. 9.40. Процессор включает в себя

шесть блоков: выборки команд, декодирования

команд, диспетчеризации команд,

распределения команд пф

функциональным

блокам, блок исполнения и блок обновления

состояния.

Рис.

9.40.

Архитектура суперскалярного процессора

Блок

выборки команд извлекает

команды из основной памяти через

кэш-память команд. Этот блок хранит

несколько значений счетчика команд и

обрабатывает команды условного перехода.

Блок

декодирования расшифровывает

код операции, содержащийся в извлеченных

из кэш-памяти командах. В некоторых

суперскалярных, процессорах, например

в микропроцессорах фирмы Intel,

блоки выборки и декодирования совмещены.

Блоки

диспетчеризации и распределения

взаимодействуют

между собой и в совокупности играют в

суперскалярном процессоре роль

контроллера трафика. Оба блока хранят

очереди декодированных команд. Очередь

блока распределения часто рассредоточивается

по несколько самостоятельным буферам

— накопителям команд или схемам

резервирования (reservation

station),-

предназначенным для хранения команд,

которые уже декодированы, но еще не

выполнены. Каждый накопитель команд

связан со своим функциональным блоком

(ФБ), поэтому число накопителей обычно

равно числу ФБ, но если в процессоре

используется несколько однотипных ФБ,

то им придается общий накопитель. По

отношению к блоку диспетчеризации

накопители команд выступают в роли

виртуальных функциональных устройств.

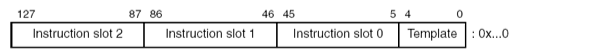

Оба вида очередей показаны на рис. 9.41

[234]. В некоторых суперскалярных процессорах

они объединены в единую очередь.

Рис.

9.41.

Очереди диспетчеризации и распределения

В

дополнение к очереди, блок диспетчеризации

хранит также список свободных

функциональных блоков, называемый табло

(Scoreboard).

Табло используется для отслеживания

состояния очереди распределения. Один

раз за цикл блок диспетчеризации

извлекает команды из своей очереди,

считывает из памяти или регистров

операнды этих команд, после чего, в

зависимости от состояния табло, помещает

команды и значения операндов в очередь

распределения. Эта операция называется

выдачей

команд. Блок

распределения в каждом цикле проверяет

каждую команду в своих очередях на

наличие всех необходимых для ее выполнения

операндов и при положительном ответе

начинает выполнение таких команд в

соответствующем функциональном блоке.

Блок

исполнения состоит

из набора функциональных блоков.

Примерами ФБ могут служить целочисленные

операционные блоки, блоки умножения и

сложения с плавающей запятой, блок

доступа к памяти. Когда исполнение

команды завершается, ее результат

записывается и анализируется блоком

обновления состояния,

который

обеспечивает учет полученного результата

теми командами в очередях распределения,

где этот результат выступает в качестве

одного из операндов.

Как

было отмечено ранее, суперскалярность

предполагает параллельную работу

максимального числа исполнительных

блоков, что возможно лишь при односменном

выполнении нескольких скалярных команд.

Последнее условие хорошо сочетается с

конвейерной обработкой, при этом

желательно, чтобы в суперскалярном

процессоре было несколько конвейеров,

например два или три.

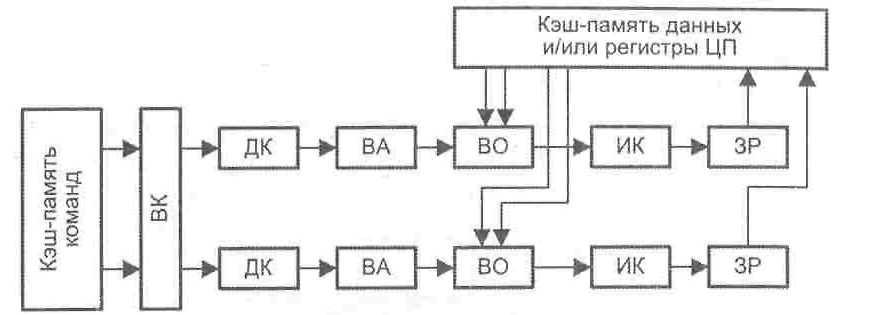

Подобный

подход реализован в микропроцессоре

Intel

Pentium,

где имеются

два

конвейера, каждый со своим АЛУ (рис.

9.42). Отметим, что здесь, в отличие от

стандартного конвейера, в каждом цикле

необходимо производить выборку более

чем одной команды. Соответственно,

память ВМ должна допускать одповременное

считывание нескольких команд и операндов,

что чаще всего обеспечивается за

счет

ее модульного построения.

Рис.

9.42. Суперскалярный

процессор с двумя конвейерами

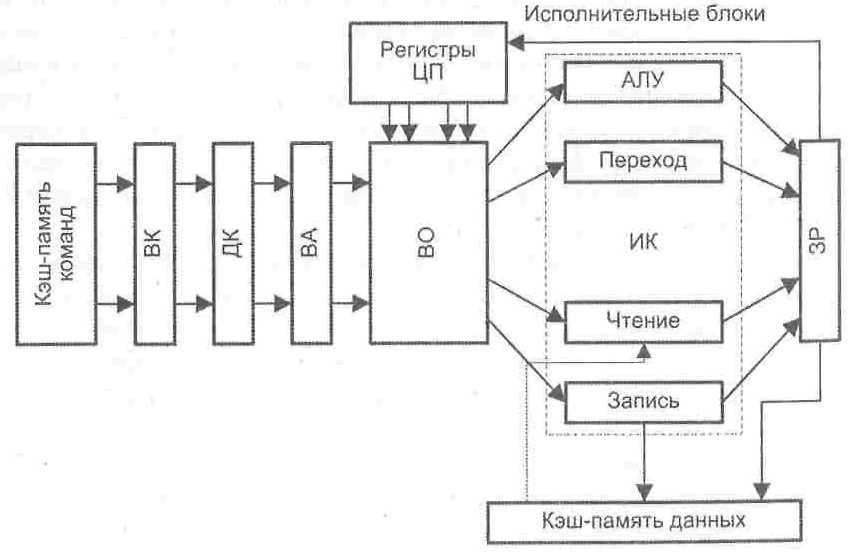

Более

интегрированный подход к построению

суперскалярного конвейера показан на

рис. 9.43. Здесь блок выборки (ВК) извлекает

из памяти более одной команды и передает

их через ступени декодирования команды

и вычисления адресов операндов в блок

выборки операндов (ВО). Когда операнды

становятся доступными, команды

распределяются по соответствующим

исполнительным блокам. Обратим внимание,

что операции «Чтение», «Запись» и

«Переход» реализуются самостоятельными

исполнительными блоками. Подобная форма

суперскалярного процессора используется

в микропроцессорах Pentium

II

и Pentium

III

фирмы Intel,

а форма с тремя конвейерами — в

микропроцессоре Athlon

фирмы AMD.

Рис.

9.43. Суперскалярный

конвейер со специализированными

исполнительными блока

По

разным оценкам, применение суперскалярного

подхода приводит к повышению

производительности ВМ в пределах от

1,8 до 8 раз.

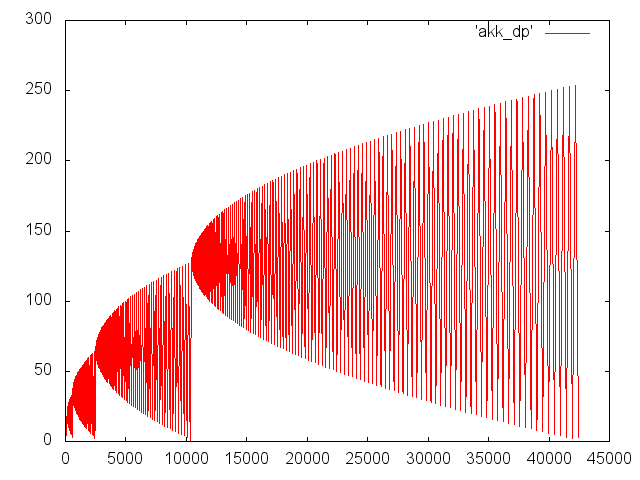

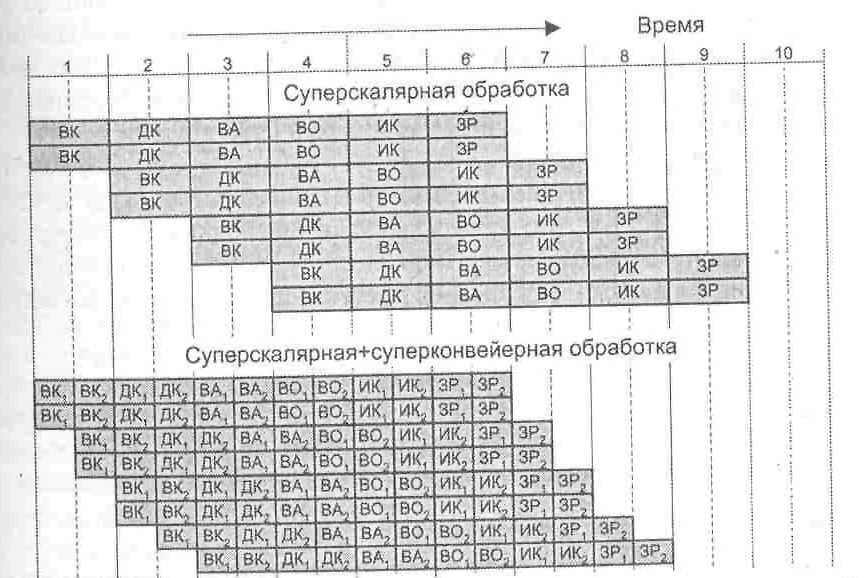

Для

сравнения эффективности суперскалярного

и суперконвейерного режима рис. 9.44

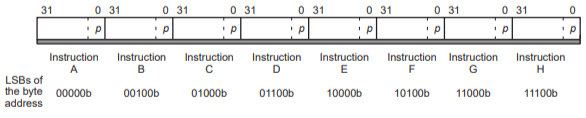

показан процесс выполнения восьми

последовательных скалярных команд.

Верхняя диаграмма иллюстрирует

суперскалярный конвейер, обеспечивающий

каждом тактовом периоде одновременную

обработку двух команд. Отметим, что

возможны суперскалярные конвейеры, где

одновременно обрабатывается большее

количество команд.

Рис.

9.44. Сравнение

суперскалярного и суперконвейерного

подходов

Рис.

9.45.

Сравнение эффективности стандартной

суперскалярной и совмещенной схем

суперскалярных

вычислений

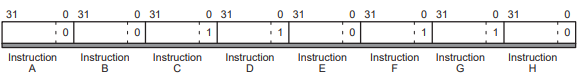

В

процессорах некоторых ВМ реализованы

как суперскалярность, так и

суперконвейеризация (рис. 9.45). Такое

совмещение имеет место в микропроцессора

Athlon

и Duron

фирмы AMD,

причем охватывает оно не только конвейер

команд, но и блок обработки чисел в форме

с плавающей запятой.

Суперскалярный процессор — Superscalar processor

«Superscaler» перенаправляется сюда. Информацию о системной плате Sega arcade см. В разделе Sega Super Scaler .

Простой суперскалярный конвейер. Посредством выборки и отправки двух инструкций за раз можно выполнить максимум две инструкции за цикл. (IF = выборка инструкции, инструкции, EX = выполнение, MEM = доступ к памяти, WB = обратная запись в регистр, i = номер инструкции, t = цикл часов [то есть время])

Суперскалярная процессор является процессором , который реализует форма параллелизма называется инструкция уровня параллелизма в одном процессоре. В отличие от скалярного процессора, который может выполнять не более одной отдельной инструкции за такт, суперскалярный процессор может выполнять более одной инструкции в течение тактового цикла, одновременно отправляя несколько инструкций различным исполнительным блокам на процессоре. Следовательно, он обеспечивает большую пропускную способность (количество инструкций, которые могут быть выполнены за единицу времени), чем это было бы возможно при заданной тактовой частоте . Каждый исполнительный блок не является отдельным процессором (или ядром, если процессор является многоядерным ), а является исполнительным ресурсом в пределах одного ЦП, например, арифметико-логическим блоком .

В таксономии Флинна одноядерный суперскалярный процессор классифицируется как процессор SISD (Single Instruction stream, Single Data stream), хотя одноядерный суперскалярный процессор, который поддерживает короткие векторные операции, может быть классифицирован как SIMD (Single Instruction stream, Multiple Data stream). потоки). Многоядерный суперскалярная процессор классифицируется как MIMD процессора (несколько потоков Инструкции, множество потоков данных).

Хотя суперскалярный ЦП обычно также является конвейерным , суперскалярное и конвейерное выполнение считаются различными методами повышения производительности. Первый выполняет несколько инструкций параллельно с использованием нескольких исполнительных модулей, тогда как последний выполняет несколько инструкций в одном и том же исполнительном модуле параллельно, разделяя исполнительный модуль на разные фазы.

Суперскалярная техника традиционно связана с несколькими отличительными характеристиками (в пределах данного ЦП):

- Инструкции выдаются из последовательного потока команд

- ЦП динамически проверяет зависимости данных между инструкциями во время выполнения (по сравнению с проверкой программного обеспечения во время компиляции ).

- ЦП может выполнять несколько инструкций за такт

Содержание

- 1 История

- 2 Скаляр в суперскаляр

- 3 Ограничения

- 4 альтернативы

- 5 См. Также

- 6 Ссылки

- 7 Внешние ссылки

Seymour Cray «s CDC 6600 с 1966 часто упоминается как первый суперскалярного дизайн. IBM System / 360 Model 91 1967 года был еще одним суперскалярным мэйнфреймом. Микропроцессоры Motorola MC88100 (1988), Intel i960 CA (1989) и AMD 29000 серии 29050 (1990) были первыми коммерческими однокристальными суперскалярными микропроцессорами. Микропроцессоры RISC, подобные этим, были первыми, в которых реализовано суперскалярное исполнение, потому что в архитектуре RISC отсутствуют транзисторы и площадь кристалла, которая может использоваться для включения нескольких исполнительных блоков (именно поэтому проекты RISC были быстрее, чем проекты CISC в 1980-х и в 1990-х годах).

За исключением ЦП, используемых в маломощных приложениях, встроенных системах и устройствах с питанием от батарей , практически все ЦП общего назначения, разработанные примерно с 1998 г., являются суперскалярными.

Р5 Pentium был первым суперскалярная x86 процессор; Nx586 , P6 Pentium Pro и AMD K5 были одними из первых конструкций, расшифровывает x86 -Инструкция асинхронно в динамический микрокод -like микроопераций последовательностей до фактического исполнения на суперскалярную микроархитектуре ; это открыло возможность для динамического планирования буферизованных частичных инструкций и позволило извлечь больше параллелизма по сравнению с более жесткими методами, используемыми в более простом P5 Pentium ; это также упростило спекулятивное исполнениеи позволил более высокие тактовые частоты по сравнению с такими конструкциями, как усовершенствованный Cyrix 6×86 .

Скаляр в суперскаляр

Самые простые процессоры — это скалярные процессоры. Каждая инструкция, выполняемая скалярным процессором, обычно манипулирует одним или двумя элементами данных одновременно. Напротив, каждая инструкция, выполняемая векторным процессором, работает одновременно со многими элементами данных. Аналогия — разница между скалярной и векторной арифметикой. Суперскалярный процессор представляет собой смесь двух. Каждая инструкция обрабатывает один элемент данных, но в каждом ЦП есть несколько исполнительных блоков, поэтому несколько инструкций могут обрабатывать отдельные элементы данных одновременно.

В суперскалярном дизайне ЦП упор делается на повышение точности диспетчера инструкций и на возможность постоянного использования нескольких исполнительных модулей. Это становится все более важным по мере увеличения количества единиц. В то время как ранние суперскалярные процессоры имели бы два ALU и один FPU , более поздний дизайн, такой как PowerPC 970, включает четыре ALU, два FPU и два модуля SIMD. Если диспетчер не может поддерживать все эти устройства с инструкциями, производительность системы будет не лучше, чем у более простой и дешевой конструкции.

Суперскалярный процессор обычно поддерживает скорость выполнения, превышающую одну инструкцию за машинный цикл . Но простая одновременная обработка нескольких инструкций не делает архитектуру суперскалярной, поскольку конвейерные , многопроцессорные или многоядерные архитектуры также достигают этого, но с другими методами.

В суперскалярном ЦП диспетчер считывает инструкции из памяти и решает, какие из них могут выполняться параллельно, отправляя каждое из нескольких исполнительных блоков, содержащихся внутри одного ЦП. Следовательно, можно представить себе суперскалярный процессор, имеющий несколько параллельных конвейеров, каждый из которых обрабатывает команды одновременно из одного потока команд.

Содержание

| Архитектура | Первая реализация | Год | Разработчик | Другие разработчики суперскалярных ЭВМ на данной архитектуре | Примечание |

|---|---|---|---|---|---|

| CDC 6600 | CDC 6600 | 1964 | Control Data Corporation | Конвейер исполнения команд, несколько исполнительных устройств (но не конвейеризованных). | |

| CDC 7600 [источник не указан 4342 дня] | CDC 7600 | 1969 | Control Data Corporation | Полная конвейеризация — и исполнения команд, и самих исполнительных устройств. | |

| IBM 360/91 [источник не указан 4342 дня] | IBM 360/91 | 1967 | IBM | Полная конвейеризация с динамическим переименованием регистров, исполнением команд не в очередности их поступления и предсказанием переходов | |

| Эльбрус | Эльбрус-1 | 1979 | ИТМиВТ | ||

| i960 | i960 | 1988 | Intel | ||

| Am29000 | Am29050 | 1990 | AMD | ||

| SPARC | SuperSPARC | 1992 | Sun Microsystems | Fujitsu, МЦСТ | |

| m88k | MC88110 | 1992 | Motorola | ||

| x86 | Pentium | 1993 | Intel | AMD, VIA | |

| MIPS | R8000 | 1994 | MIPS Technologies | Toshiba | |

| ARM | Cortex A8 | ARM |

В суперскалярных вычислительных машинах используется ряд методов для ускорения вычислений, характерных прежде всего для них, однако такие методики могут использоваться и в других типах архитектур:

- Внеочередное исполнение

- Переименование регистров

- Объединение нескольких команд в одну

Также используются общие методики увеличения производительности, применяемые и в других типах вычислительных машин:

Альтернативы [ править ]

В совокупности эти ограничения приводят к исследованию альтернативных архитектурных изменений, таких как очень длинное командное слово (VLIW), явно параллельное вычисление команд (EPIC), одновременная многопоточность (SMT) и многоядерные вычисления .

С VLIW обременительная задача проверки зависимостей аппаратной логикой во время выполнения снимается и делегируется компилятору . Явно параллельное вычисление инструкций (EPIC) похоже на VLIW с дополнительными инструкциями предварительной выборки из кэша.

Одновременная многопоточность (SMT) — это метод повышения общей эффективности суперскалярных процессоров. SMT позволяет выполнять несколько независимых потоков, чтобы лучше использовать ресурсы, предоставляемые современными архитектурами процессоров.

Суперскалярные процессоры отличаются от многоядерных процессоров тем, что несколько исполнительных блоков не являются целыми процессорами. Один процессор состоит из исполнительных модулей с более мелкой структурой, таких как ALU , целочисленный умножитель , целочисленный сдвигатель, FPU и т. Д. Может быть несколько версий каждого исполнительного модуля, чтобы обеспечить выполнение множества инструкций параллельно. Это отличается от многоядерного процессора, который одновременно обрабатывает инструкции из нескольких потоков, по одному потоку на процессор (называемый «ядром»). Он также отличается от конвейерного процессора , где несколько инструкций могут одновременно находиться на разных стадиях выполнения,конвейерная мода.

Различные альтернативные методы не исключают друг друга — они могут (и часто комбинируются) в одном процессоре. Таким образом, возможен многоядерный ЦП, где каждое ядро является независимым процессором, содержащим несколько параллельных конвейеров, причем каждый конвейер является суперскалярным. Некоторые процессоры также имеют возможность вектора .

Содержание

Сеймур Крейс CDC 6600 с 1966 года часто упоминается как первая суперскалярная конструкция. 1967 год IBM System / 360 Модель 91 был еще одним суперскалярным мэйнфреймом. Motorola MC88100 (1988), Intel i960CA (1989) и 29000 драмМикропроцессоры серии 29050 (1990) были первыми коммерческими однокристальными суперскалярными микропроцессорами. RISC микропроцессоры, подобные этим, были первыми, у которых было суперскалярное исполнение, потому что RISC-архитектура освобождает транзисторы и площадь кристалла, которая может использоваться для включения нескольких исполнительных блоков (вот почему RISC-конструкции были быстрее, чем CISC дизайнов с 1980-х по 1990-е годы).

За исключением процессоров, используемых в малая мощность Приложения, встроенные системы, и аккумуляторустройства с питанием, по сути, все ЦП общего назначения, разработанные примерно с 1998 года, являются суперскалярными.

В P5 Pentium был первым суперскалярным процессором x86; то Nx586, P6 Pentium Pro и AMD K5 были одними из первых дизайнов, которые расшифровывают x86-инструкции асинхронно в динамические микрокод-подобно микрооперация последовательности до фактического выполнения на суперскалярном микроархитектура; это открыло для динамического планирования буферизованных частичный инструкций и позволил извлечь больше параллелизма по сравнению с более жесткими методами, используемыми в более простых P5 Pentium; это также упростило спекулятивное исполнение и позволили более высокие тактовые частоты по сравнению с такими конструкциями, как усовершенствованный Cyrix 6×86.

Содержание

Сеймур Крейс CDC 6600 с 1966 года часто упоминается как первая суперскалярная конструкция. 1967 год IBM System / 360 Модель 91 был еще одним суперскалярным мэйнфреймом. Motorola MC88100 (1988), Intel i960CA (1989) и 29000 драмМикропроцессоры серии 29050 (1990) были первыми коммерческими однокристальными суперскалярными микропроцессорами. RISC микропроцессоры, подобные этим, были первыми, у которых было суперскалярное исполнение, потому что RISC-архитектура освобождает транзисторы и площадь кристалла, которая может использоваться для включения нескольких исполнительных блоков (вот почему RISC-конструкции были быстрее, чем CISC дизайнов с 1980-х по 1990-е годы).

За исключением процессоров, используемых в малая мощность Приложения, встроенные системы, и аккумуляторустройства с питанием, по сути, все ЦП общего назначения, разработанные примерно с 1998 года, являются суперскалярными.

В P5 Pentium был первым суперскалярным процессором x86; то Nx586, P6 Pentium Pro и AMD K5 были одними из первых дизайнов, которые расшифровывают x86-инструкции асинхронно в динамические микрокод-подобно микрооперация последовательности до фактического выполнения на суперскалярном микроархитектура; это открыло для динамического планирования буферизованных частичный инструкций и позволил извлечь больше параллелизма по сравнению с более жесткими методами, используемыми в более простых P5 Pentium; это также упростило спекулятивное исполнение и позволили более высокие тактовые частоты по сравнению с такими конструкциями, как усовершенствованный Cyrix 6×86.

Содержание