Устройство процессора.

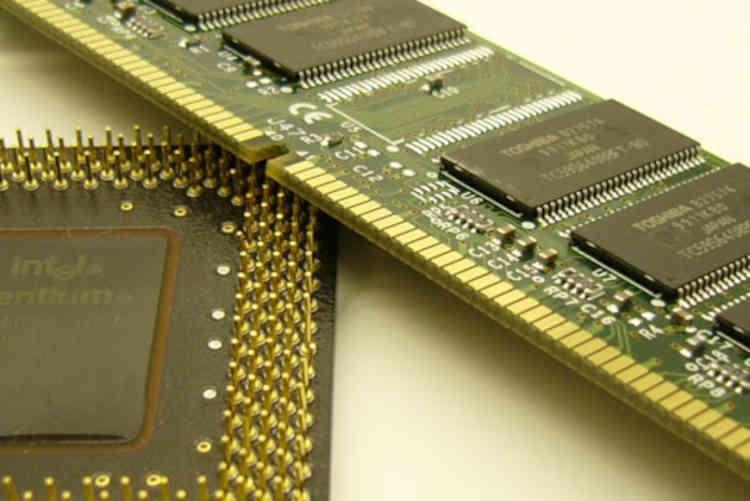

Процессор – это

основное устройство ЭВМ, выполняющее

логические и арифметические операции,

и осуществляющее управление всеми

компонентами ЭВМ. Процессор представляет

собой миниатюрную тонкую кремниевую

пластинку прямоугольной формы, на

которой размещается огромное количество

транзисторов, реализующих все функции,

выполняемые процессором. Кремневая

пластинка – очень хрупкая, а так как ее

любое повреждение приведет к выходу из

строя процессора, то она помещается в

пластиковый или керамический корпус.

Содержание.

1.

Введение

2.

Ядро процессора

2.1.

Принцип работы ядра процессора

2.2.

Способы повышения производительности

ядра процессора

2.2.1.

Конвейеризация

2.2.2.

Суперскалярность

2.2.3.

Параллельная обработка данных

2.2.4.

Технология Hyper-threading

2.2.5.

Технология Turbo Boost.

2.2.6.

Эффективность выполнения команд.

2.3

Способы снижения энергопотребления

ядра процессора

3.

КЭШ-память

1. Введение.

Современный

процессор – это сложное и высокотехнологическое

устройство, включающее в себя все самые

последние достижения в области

вычислительной техники и сопутствующих

областей науки.

Большинство

современных процессоров состоит из:

-

одного или

нескольких ядер, осуществляющих

выполнение всех инструкций; -

нескольких уровней

КЭШ-памяти (обычно, 2 или три уровня),

ускоряющих взаимодействие процессора

с ОЗУ; -

контроллера ОЗУ;

-

контроллера

системной шины (DMI, QPI, HT и т.д.);

И характеризуется

следующими параметрами:

-

типом микроархитектуры;

-

тактовой частотой;

-

набором выполняемых

команд; -

количеством

уровней КЭШ-памяти и их объемом; -

типом и скоростью

системной шины; -

размерами

обрабатываемых слов; -

наличием или

отсутствием встроенного контроллера

памяти; -

типом поддерживаемой

оперативной памяти; -

объемом адресуемой

памяти; -

наличием или

отсутствием встроенного графического

ядра; -

энергопотреблением.

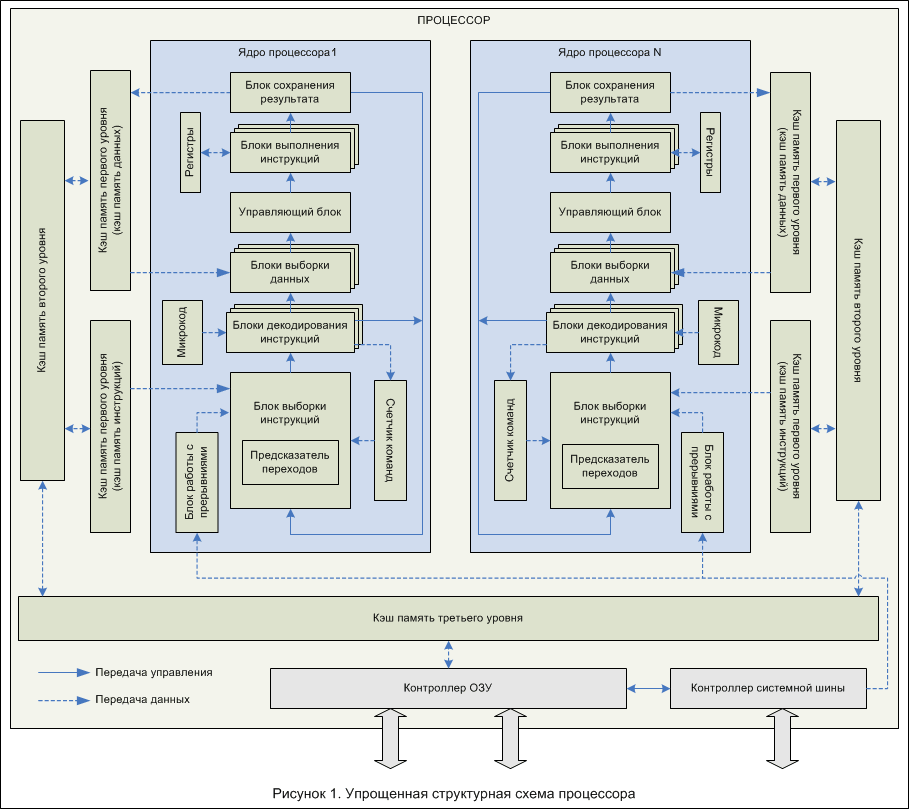

Упрощенная

структурная схема современного

многоядерного процессора представлена

на рисунке 1.

Начнем обзор

устройства процессора с его основной

части – ядра.

2. Ядро процессора.

Ядро процессора

– это его основная часть, содержащая

все функциональные блоки и осуществляющая

выполнение всех логических и арифметических

операций.

На рисунке 1

приведена структурная схема устройства

ядра процессора. Как видно на рисунке,

каждое ядро процессора состоит из

нескольких функциональных блоков:

-

блока выборки

инструкций; -

блоков декодирования

инструкций; -

блоков выборки

данных; -

управляющего

блока; -

блоков выполнения

инструкций; -

блоков сохранения

результатов; -

блока работы с

прерываниями; -

ПЗУ, содержащего

микрокод; -

набора регистров;

-

счетчика команд.

Блок

выборки инструкций осуществляет

считывание инструкций по адресу,

указанному в счетчике команд. Обычно,

за такт он считывает несколько инструкций.

Количество считываемых инструкций

обусловлено количеством блоков

декодирования, так как необходимо на

каждом такте работы максимально загрузить

блоки декодирования. Для того чтобы

блок выборки инструкций работал

оптимально, в ядре процессора имеется

предсказатель переходов.

Предсказатель

переходов пытается

определить, какая последовательность

команд будет выполняться после совершения

перехода. Это необходимо, чтобы после

условного перехода максимально нагрузить

конвейер ядра процессора.

Блоки

декодирования,

как понятно из названия, – это блоки,

которые занимаются декодированием

инструкций, т.е. определяют, что надо

сделать процессору, и какие дополнительные

данные нужны для выполнения инструкции.

Задача эта для большинства современных

коммерческих процессоров, построенных

на базе концепции CISC, – очень сложная.

Дело в том, что длина инструкций и

количество операндов – нефиксированные,

и это сильно усложняет жизнь разработчикам

процессоров и делает процесс декодирования

нетривиальной задачей.

Часто отдельные

сложные команды приходится заменять

микрокодом – серией простых инструкций,

в совокупности выполняющих то же

действие, что и одна сложная инструкция.

Набор микрокода прошит в ПЗУ, встроенном

в процессоре. К тому же микрокод упрощает

разработку процессора, так как отпадает

надобность в создании сложноустроенных

блоков ядра для выполнения отдельных

команд, да и исправить микрокод гораздо

проще, чем устранить ошибку в

функционировании блока.

В современных

процессорах, обычно, бывает 2-4 блока

декодирования инструкций, например, в

процессорах Intel Core 2 каждое ядро содержит

по два таких блока.

Блоки

выборки данных осуществляют

выборку данных из КЭШ-памяти или ОЗУ,

необходимых для выполнения текущих

инструкций. Обычно, каждое процессорное

ядро содержит несколько блоков выборки

данных. Например, в процессорах Intel Core

используется по два блока выборки данных

для каждого ядра.

Управляющий

блок на

основании декодированных инструкций

управляет работой блоков выполнения

инструкций, распределяет нагрузку между

ними, обеспечивает своевременное и

верное выполнение инструкций. Это один

из наиболее важных блоков ядра процессора.

Блоки

выполнения инструкций включают

в себя несколько разнотипных блоков:

ALU – арифметическое

логическое устройство;

FPU – устройство

по выполнению операций с плавающей

точкой;

Блоки для обработки

расширения наборов инструкций.

Дополнительные инструкции используются

для ускорения обработки потоков данных,

шифрования и дешифрования, кодирования

видео и так далее. Для этого в ядро

процессора вводят дополнительные

регистры и наборы логики. На данный

момент наиболее популярными расширениями

наборов инструкция являются:

MMX (Multimedia Extensions) –

набор инструкций, разработанный компанией

Intel, для ускорения кодирования и

декодирования потоковых аудио и

видео-данных;

SSE (Streaming SIMD

Extensions) – набор инструкций, разработанный

компанией Intel, для выполнения одной и

той же последовательности операций над

множеством данных с распараллеливанием

вычислительного процесса. Наборы команд

постоянно совершенствуются, и на данный

момент имеются ревизии: SSE, SSE2, SSE3, SSSE3,

SSE4;

ATA (Application Targeted

Accelerator) – набор инструкций, разработанный

компанией Intel, для ускорения работы

специализированного программного

обеспечения и снижения энергопотребления

при работе с такими программами. Эти

инструкции могут использоваться,

например, при расчете контрольных сумм

или поиска данных;

3DNow – набор

инструкций, разработанный компанией

AMD, для расширения возможностей набора

инструкций MMX;

AES (Advanced Encryption

Standard) – набор инструкций, разработанный

компанией Intel, для ускорения работы

приложений, использующих шифрование

данных по одноименному алгоритму.

Блок

сохранения результатов обеспечивает

запись результата выполнения инструкции

в ОЗУ по адресу, указанному в обрабатываемой

инструкции.

Блок

работы с прерываниями. Работа

с прерываниями – одна из важнейших

задач процессора, позволяющая ему

своевременно реагировать на события,

прерывать ход работы программы и

выполнять требуемые от него действия.

Благодаря наличию прерываний, процессор

способен к псевдопараллельной работе,

т.е. к, так называемой, многозадачности.

Обработка прерываний

происходит следующим образом. Процессор

перед началом каждого цикла работы

проверяет наличие запроса на прерывание.

Если есть прерывание для обработки,

процессор сохраняет в стек адрес

инструкции, которую он должен был

выполнить, и данные, полученные после

выполнения последней инструкции, и

переходит к выполнению функции обработки

прерывания.

После окончания

выполнения функции обработки прерывания,

из стека считываются сохраненные в него

данные, и процессор возобновляет

выполнение восстановленной задачи.

Регистры –

сверхбыстрая оперативная память (доступ

к регистрам в несколько раз быстрее

доступа к КЭШ-памяти) небольшого объема

(несколько сотен байт), входящая в состав

процессора, для временного хранения

промежуточных результатов выполнения

инструкций. Регистры процессора делятся

на два типа: регистры общего назначения

и специальные регистры.

Регистры общего

назначения используются при выполнении

арифметических и логических операций,

или специфических операций дополнительных

наборов инструкций (MMX, SSE и т.д.).

Регистры специального

назначения содержат системные данные,

необходимые для работы процессора. К

таким регистрам относятся, например,

регистры управления, регистры системных

адресов, регистры отладки и т.д. Доступ

к этим регистрам жестко регламентирован.

Счетчик

команд –

регистр, содержащий адрес команды,

которую процессор начнет выполнять на

следующем такте работы.

Соседние файлы в папке ТСИ

- #

- #

- #

- #

- #

- #

Время на прочтение

2 мин

Количество просмотров 112K

Simple CPU — маленький урок, который знакомит новичка с ключевыми понятиями информатики. Хотя урок далеко не полный и предназначен для «самых маленьких», но даже образованному человеку приятно видеть, насколько доступно и элегантно можно изложить сложный материал.

Урок состоит из 8 интерактивных примеров.

1. Бинарное счисление.

2. Логические операции на примере штриха Шеффера (NAND gate).

Штрих Шеффера (NAND gate)

3. Триггер. Демонстрирует, как хранится информация в компьютере. Верхний переключатель изменяет значение бита, а нижний включает/отключает хранение.

D-триггер (триггер задержки)

Восемь триггеров сохраняют 1 байт информации.

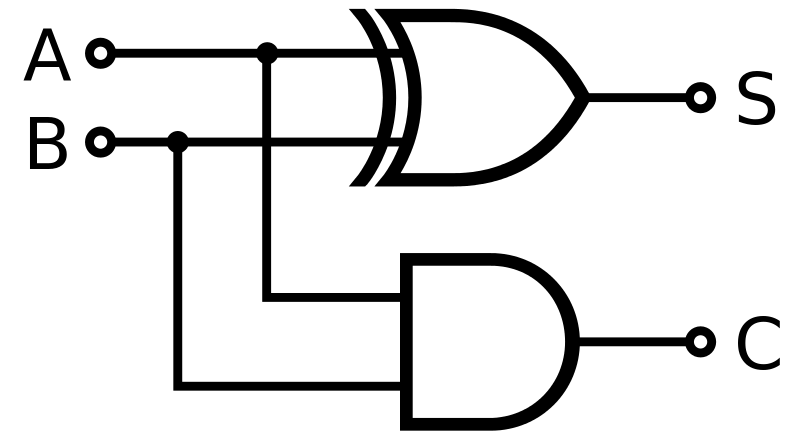

4. Логические операции AND, OR, XOR. Щёлкая мышкой по входящим значениям, можно наглядно посмотреть, как они работают.

Что делать с числами, которые мы храним в памяти?

5. На схеме показано устройство под названием сумматор, которое складывает два бита. Если нужно сложить несколько бит, то последовательно используется несколько сумматоров: вход одного (carry in) подключается к выходу другого (carry out).

Опять же, это интерактивная схема.

Далее, как из калькулятора сделать компьютер?

6. Программирование.

С точки зрения CPU, программа не отличается от данных в том смысле, что здесь такой же двоичный код. Но он воспринимаются как инструкции. Например:

| Инструкция | Код | |

| «Добавить одно число к другому» | 00000001 | |

| «Вычесть одно число из другого» | 00000010 |

У каждого байта в памяти есть свой адрес, так что мы можем обратиться к CPU и попросить сделать что-то с конкретным байтом. Например, если нужно обратиться к ячейке памяти № 5, то мы указываем её адрес 00000101.

Таким образом, команда «Сложить число в ячейке памяти № 5 с числом в ячейке памяти № 7 транслируется в машинный код:

00000001 00000101 00000111

(сложить)(адрес № 5)(адрес № 7)

7. Набор инструкций CPU.

8. Эмулятор CPU.

Здесь автор предлагает поиграться с простым эмулятором процессора, указывая инструкции в отдельных ячейках памяти. При этом инструкции меняют значение других ячеек, где тоже хранятся инструкции. Можно придумать забавные рекурсии. Компьютер понимает три инструкции: сложение, вычитание и перемещение данных из одной ячейки в другую.

Simple CPU на Github

Об авторе

P.S. Интересно, что проект родился на форумах Reddit, а его автор — только что закончивший школу пользователь r00nk. Поскольку r00nk двоечник, его сейчас не берут ни в один хороший колледж, так что он пытается пройти курс информатики самостоятельно, попутно изучая OpenGL.

ЦП означает центральный процессор или «центральный процессор»; если говорить человеческим языком, то ЦП — это центральный процессор устройства. Любое современное вычислительное устройство (смартфон, планшет, компьютер, телевизор, сервер и т д.) имеет свой центральный процессор, отвечающий за общую функциональность и правильную работу устройства.

В широком смысле ЦП или процессор — это небольшой компонент устройства, функции которого заключаются в обработке логических и вычислительных операций, а также в управлении и контроле функциональности других компонентов устройства. Процессор — это мозг и сердце любого вычислительного устройства, поэтому он считается самым важным компонентом всех вычислительных устройств.

Процессор — что это

Все устройства имеют разные процессоры, но если рассматривать процессор компьютера, то визуально процессор представляет собой небольшой квадрат плоской формы со стороной около 5 см. Внутри процессора находится множество разъемов, которыми он подключается к основанию платы. От мощности центрального процессора будет зависеть скорость обработки инструкций и производительность других компонентов компьютера. Например, если вы приобрели мощную видеокарту для своего компьютера, вы не увидите ее полной мощности, потому что у вашего компьютера слабый процессор.

Назначение процессора в компьютере

Что такое ЦП (центральный процессор) в компьютере? Если процессор в компьютере – это мозг, то уже понятно, что основная деятельность процессора – это управление всеми вычислительными компонентами и операциями компьютера, от простых расчетов на калькуляторе до запуска “тяжелых” программ, того же компьютера игры или 3D-редакторы.

Если немного «вникнуть» в назначение процессора, то можно выделить следующие его функции:

- получать данные из оперативной памяти и выполнять с ними необходимые операции;

- генерировать сигналы и команды для управления внутренними компонентами или внешними устройствами, подключенными к компьютеру;

- временное хранение в собственной памяти информации о выполненных операциях или отданных командах;

- обрабатывать запросы от внешних устройств или внутренних компонентов компьютера;

- и так далее

Из чего состоит процессор

Центральный процессор не является конечной деталью, он также собирается из мелких, но важных деталей. Процессор можно разделить на 3 компонента:

- Ядро процессора. Именно в нем больше всего падает функциональность процессора. Я занимаюсь декодированием, чтением, выполнением и отправкой инструкций другим компонентам или, наоборот, от других компонентов. Ядро может выполнять только одну инструкцию за раз, хотя и за сотые доли секунды. Поэтому, если процессор компьютера состоит из одного ядра, компьютер будет выполнять все команды последовательно и по очереди. В наши дни редко можно увидеть одноядерные компьютеры, потому что они слишком громоздки для современных пользовательских команд. А вот процессор с 2, 3, 4 и более ядрами — не редкость.

- Запоминающее устройство. У каждого процессора есть своя небольшая память, необходимая ему для работы. Память процессора состоит из двух частей: одна часть нужна для «запоминания» текущих операций, а другая часть памяти — это кэш-память, в которой хранятся часто выполняемые инструкции. Доступ к собственному e-sh будет быстрее, чем доступ к оперативной памяти компьютера, поэтому объем электронной памяти влияет на скорость и производительность процессора.

- Шины — это пути, по которым команды передаются внутри процессора.

Чем характеризуется процессор

Важнейшей характеристикой любого процессора является его производительность. Однако производительность процессора зависит от 2-х его параметров:

- Тактовая частота – это количество операций, выполняемых в единицу времени. Чем выше эта частота, тем быстрее «думает» процессор. Частота рассчитывается в мегагерцах x (МГц) или гигагерцах x (ГГц).

- Разрядность — это количество информации, которую процессор может передать за один цикл; измеряется в битах. Все мы слышим о 32-битных и 64-битных компьютерах — вот и все.

Виды и производители процессоров

На самом деле процессоров существует великое множество, а производителей процессоров можно пересчитать по пальцам одной руки. Процессоры делаются разные для разных устройств. Но даже если принять во внимание только одно устройство — компьютер, здесь нас ждет огромный ассортимент — от более «слабых» одноядерных процессоров для офисной работы до многоядерных процессоров, предназначенных для сложных научных расчетов.

Среди производителей процессоров для компьютеров и ноутбуков наиболее известны 2 производителя: Intel и AMD. Главное отличие процессоров от этих компаний не в количестве ядер или производительности, а в уникальной архитектуре. То есть эти компании разрабатывают процессоры по разным принципам, поэтому у процессоров обоих производителей есть свои плюсы и минусы, о которых мы сейчас говорить не будем, потому что это тема для отдельной статьи.

Для смартфонов и планшетов наиболее известными производителями процессоров являются NVIDIA, Qualcomm и Apple.

Заключение

Что такое процессор в компьютере? Центральный процессор — это то, без чего компьютер не может функционировать. Простейшая операция на компьютере выполняется только командой процессора и никак иначе. Производительность компьютера напрямую связана с производительностью процессора, поэтому перед покупкой компьютера важно выбрать процессор, соответствующий вашим потребностям.

Как работает процессор?

Инструмент легче, чем машина. Часто инструмент работает вручную, а машина приводится в действие паром или животным.

Компьютер тоже можно назвать машиной, но вместо пара в нем электричество. Но программирование сделало компьютер таким же простым, как любой инструмент.

Процессор — это сердце/мозг любого компьютера. Основное внимание в нем уделяется арифметическим и логическим операциям, и прежде чем погрузиться в процессорные дебри, необходимо разобраться в его основных компонентах и в том, как они работают.

Два основных компонента процессора

Устройство управления

Блок управления (CU) помогает процессору контролировать и выполнять инструкции. CU точно сообщает компонентам, что делать. В зависимости от инструкций он координируется с другими частями компьютера, включая второй основной компонент — арифметико-логическое устройство (АЛУ). Все инструкции сначала поступают на управляющее устройство.

Существует два типа реализации CU:

- БУ на базе проводных блоков управления. Характер работы определяется внутренней электрической структурой: устройство на печатной плате или кристалле. Следовательно, модификация такого блока управления без физического вмешательства невозможна.

- БУ с микропрограммируемым управлением (в англ microprogrammable control tools). Его можно запрограммировать для определенных целей. Программная часть хранится в памяти БУ.

CU с жесткой логикой быстрее, но CU, управляемый микропрограммой, имеет более гибкую функциональность.

Арифметико-логическое устройство

Это устройство, как ни странно, выполняет все арифметические и логические операции, такие как сложение, вычитание, логическое ИЛИ и т.д. АЛУ состоит из логических элементов, которые выполняют эти операции.

Большинство логических вентилей имеют два входа и один выход.

Ниже приведена схема полусумматора с двумя входами и двумя выходами. Здесь A и B — входы, S — выход, C — переход (в более высокий порядок).

Схема арифметического полусумматора

Хранение информации — регистры и память

Как было сказано выше, процессор выполняет поступающие к нему команды. Команды в большинстве случаев работают с данными, которые могут быть промежуточными, входными или выходными. Все эти данные вместе с инструкциями хранятся в регистрах и памяти.

Регистры

Регистр — это наименьшая ячейка памяти данных. Регистры состоят из триггеров (англ latches/flip-flops). Триггеры, в свою очередь, состоят из логических элементов и могут хранить 1 бит информации.

Примечание. Триггеры перевода могут быть синхронными или асинхронными. Асинхронные могут изменить свое состояние в любой момент, а синхронные только при положительном/отрицательном фронте на входе синхронизации.

По своему функциональному назначению триггеры делятся на несколько групп:

- RS-триггер: сохраняет свое состояние при нулевом уровне на обоих входах и меняет его при установке в единицу на одном из входов (Reset/Set – Reset/Set).

- JK-триггер: Идентичен RS-триггеру, за исключением того, что при подаче единиц на два входа одновременно триггер меняет свое состояние на противоположное (режим счета).

- Т-триггер: переворачивает свое состояние каждый такт на своем единственном входе.

- D-триггер: запоминает состояние входа во время синхронизации. Асинхронные D-триггеры не имеют смысла.

Оперативная память не подходит для хранения промежуточных данных, так как это замедлит работу процессора. Промежуточные данные отправляются в регистры на шине. Они могут хранить команды, выходные данные и даже адреса ячеек памяти.

Принцип работы RS-триггера

Память (ОЗУ)

ОЗУ (оперативное запоминающее устройство, англ. RAM) представляет собой большую группу этих же самых регистров, соединенных друг с другом. Память такого хранилища нестабильна и данные в ней пропадают при отключении питания. Оперативная память принимает адрес области памяти, куда будут помещены данные, сами данные и флаг записи/чтения, который активирует триггеры.

Обратите внимание, что оперативная память перевода бывает статической и динамической: SRAM и DRAM соответственно. В статической памяти ячейками являются триггеры, а в динамической памяти — конденсаторы. SRAM быстрее, а DRAM дешевле.

Команды (инструкции)

Команды — это фактические действия, которые должен выполнить компьютер. Есть несколько типов:

- Арифметика: сложение, вычитание, умножение и т.д.

- Логические: И (логическое умножение/соединение), ИЛИ (логическое сложение/дизъюнкция), отрицание и т д

- Информационные: перемещайте, вводите, экспортируйте, загружайте и сохраняйте .

- Команды перехода: перейти, если перейти, вызвать и вернуться .

- Команда остановки: стоп .

Note translate На самом деле все арифметические операции в АЛУ могут быть созданы всего из двух: сложения и изменения. Однако чем больше основных операций поддерживает АЛУ, тем быстрее оно будет работать.

Инструкции передаются компьютеру на языке ассемблера или генерируются компилятором языка высокого уровня.

В процессоре инструкции реализованы аппаратно. За один такт один основной процессор может выполнить один элементарный (базовый.

Группа инструкций обычно называется набором инструкций).

Тактирование процессора

Скорость компьютера определяется тактовой частотой его процессора. Тактовая частота: количество тактов (соответственно и исполняемых команд) в секунду.

Частота современных процессоров измеряется в ГГц (Гигагерцах). 1 ГГц = 10⁹ Гц — это миллиард операций в секунду.

Чтобы уменьшить время выполнения программы, необходимо ее оптимизировать (уменьшить) или увеличить тактовую частоту. Некоторые процессоры имеют возможность увеличения частоты (разгона процессора); однако такие действия физически влияют на процессор и часто вызывают его перегрев и выход из строя.

Выполнение инструкций

Инструкции хранятся в оперативной памяти в последовательном порядке. Для гипотетического процессора инструкция состоит из кода операции и адреса памяти/регистра. Внутри управляющего устройства имеется два регистра инструкций, в которые загружаются код инструкции и адрес выполняемой в данный момент инструкции. Процессор также имеет дополнительные регистры, в которых хранятся последние 4 бита выполненных инструкций.

Вот пример набора команд, который складывает два числа:

- НАГРУЗКА_А 8 . Эта команда сохраняет данные в оперативной памяти, например, . Первые 4 бита — код операции. Именно он определяет инструкцию. Эти данные помещаются в регистры команд CU. Команда расшифровывается в инструкции load_A: поместите данные 1000 (последние 4 бита команды) в регистр A .

- НАГРУЗКА_В 2 . Ситуация похожа на предыдущую. Это помещает число 2 (0010) в регистр B .

- АДДБА. Команда добавляет два числа (точнее, добавляет значение регистра B к регистру A). CU приказывает ALU выполнить операцию сложения и поместить результат обратно в регистр A .

- МАГАЗИН_А 23 . Мы сохраняем значение регистра A в ячейке памяти 23 .

Это операции, необходимые для сложения двух чисел.

Все данные между процессором, регистрами, памятью и устройствами ввода/вывода (устройствами ввода/вывода) передаются по шинам. Чтобы загрузить вновь обработанные данные в память, процессор помещает адрес на шину адреса и данные на шину данных. Затем нужно дать разрешение на запись в управляющую шину.

Процессор имеет механизм хранения инструкций в кэше. Как мы выяснили ранее, процессор может выполнять миллиарды инструкций в секунду. Следовательно, если бы каждая инструкция хранилась в ОЗУ, выборка заняла бы больше времени, чем обработка. Поэтому для ускорения работы процессор часть инструкций и данных хранит в кэш-памяти.

Если данные в кеше и памяти не совпадают, они помечаются грязными битами).

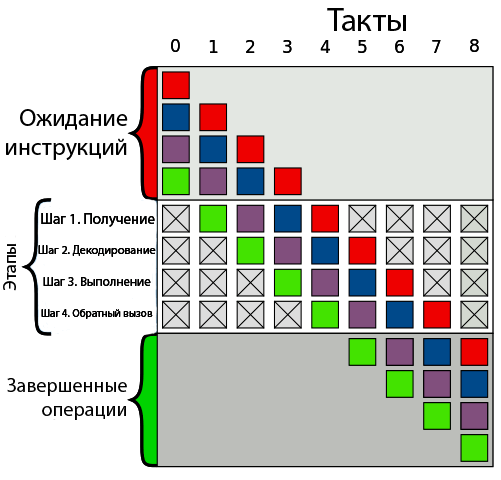

Поток инструкций

Современные процессоры могут обрабатывать несколько инструкций параллельно. Пока инструкция находится в стадии декодирования, процессор может успеть принять другую инструкцию.

Однако это решение подходит только для тех инструкций, которые не зависят друг от друга.

Если процессор многоядерный, это означает, что он на самом деле имеет несколько отдельных процессоров с некоторыми общими ресурсами, такими как кеш.

Небольшой анонс! Мы уже публиковали статью о программах, которые являются аналогом Time Machine в macOS, скоро опубликуем статью для Windows, в том числе и о программе Mozy.

Инструмент проще, чем машина. Зачастую инструментом работают руками, а машину приводит в действие паровая сила или животное.

Компьютер тоже можно назвать машиной, только вместо паровой силы здесь электричество. Но программирование сделало компьютер таким же простым, как любой инструмент.

Процессор — это сердце/мозг любого компьютера. Его основное назначение — арифметические и логические операции, и прежде чем погрузиться в дебри процессора, нужно разобраться в его основных компонентах и принципах их работы.

Два основных компонента процессора

Устройство управления

Устройство управления (УУ) помогает процессору контролировать и выполнять инструкции. УУ сообщает компонентам, что именно нужно делать. В соответствии с инструкциями он координирует работу с другими частями компьютера, включая второй основной компонент — арифметико-логическое устройство (АЛУ). Все инструкции вначале поступают именно на устройство управления.

Существует два типа реализации УУ:

- УУ на жёсткой логике (англ. hardwired control units). Характер работы определяется внутренним электрическим строением — устройством печатной платы или кристалла. Соответственно, модификация такого УУ без физического вмешательства невозможна.

- УУ с микропрограммным управлением (англ. microprogrammable control units). Может быть запрограммирован для тех или иных целей. Программная часть сохраняется в памяти УУ.

УУ на жёсткой логике быстрее, но УУ с микропрограммным управлением обладает более гибкой функциональностью.

Арифметико-логическое устройство

Это устройство, как ни странно, выполняет все арифметические и логические операции, например сложение, вычитание, логическое ИЛИ и т. п. АЛУ состоит из логических элементов, которые и выполняют эти операции.

Большинство логических элементов имеют два входа и один выход.

Ниже приведена схема полусумматора, у которой два входа и два выхода. A и B здесь являются входами, S — выходом, C — переносом (в старший разряд).

Схема арифметического полусумматора

Хранение информации — регистры и память

Как говорилось ранее, процессор выполняет поступающие на него команды. Команды в большинстве случаев работают с данными, которые могут быть промежуточными, входными или выходными. Все эти данные вместе с инструкциями сохраняются в регистрах и памяти.

Регистры

Регистр — минимальная ячейка памяти данных. Регистры состоят из триггеров (англ. latches/flip-flops). Триггеры, в свою очередь, состоят из логических элементов и могут хранить в себе 1 бит информации.

Прим. перев. Триггеры могут быть синхронные и асинхронные. Асинхронные могут менять своё состояние в любой момент, а синхронные только во время положительного/отрицательного перепада на входе синхронизации.

По функциональному назначению триггеры делятся на несколько групп:

- RS-триггер: сохраняет своё состояние при нулевых уровнях на обоих входах и изменяет его при установке единице на одном из входов (Reset/Set — Сброс/Установка).

- JK-триггер: идентичен RS-триггеру за исключением того, что при подаче единиц сразу на два входа триггер меняет своё состояние на противоположное (счётный режим).

- T-триггер: меняет своё состояние на противоположное при каждом такте на его единственном входе.

- D-триггер: запоминает состояние на входе в момент синхронизации. Асинхронные D-триггеры смысла не имеют.

Для хранения промежуточных данных ОЗУ не подходит, т. к. это замедлит работу процессора. Промежуточные данные отсылаются в регистры по шине. В них могут храниться команды, выходные данные и даже адреса ячеек памяти.

Принцип действия RS-триггера

Память (ОЗУ)

ОЗУ (оперативное запоминающее устройство, англ. RAM) — это большая группа этих самых регистров, соединённых вместе. Память у такого хранилища непостоянная и данные оттуда пропадают при отключении питания. ОЗУ принимает адрес ячейки памяти, в которую нужно поместить данные, сами данные и флаг записи/чтения, который приводит в действие триггеры.

Прим. перев. Оперативная память бывает статической и динамической — SRAM и DRAM соответственно. В статической памяти ячейками являются триггеры, а в динамической — конденсаторы. SRAM быстрее, а DRAM дешевле.

Команды (инструкции)

Команды — это фактические действия, которые компьютер должен выполнять. Они бывают нескольких типов:

- Арифметические: сложение, вычитание, умножение и т. д.

- Логические: И (логическое умножение/конъюнкция), ИЛИ (логическое суммирование/дизъюнкция), отрицание и т. д.

- Информационные:

move,input,outptut,loadиstore. - Команды перехода:

goto,if ... goto,callиreturn. - Команда останова:

halt.

Прим. перев. На самом деле все арифметические операции в АЛУ могут быть созданы на основе всего двух: сложение и сдвиг. Однако чем больше базовых операций поддерживает АЛУ, тем оно быстрее.

Инструкции предоставляются компьютеру на языке ассемблера или генерируются компилятором высокоуровневых языков.

В процессоре инструкции реализуются на аппаратном уровне. За один такт одноядерный процессор может выполнить одну элементарную (базовую) инструкцию.

Группу инструкций принято называть набором команд (англ. instruction set).

Тактирование процессора

Быстродействие компьютера определяется тактовой частотой его процессора. Тактовая частота — количество тактов (соответственно и исполняемых команд) за секунду.

Частота нынешних процессоров измеряется в ГГц (Гигагерцы). 1 ГГц = 10⁹ Гц — миллиард операций в секунду.

Чтобы уменьшить время выполнения программы, нужно либо оптимизировать (уменьшить) её, либо увеличить тактовую частоту. У части процессоров есть возможность увеличить частоту (разогнать процессор), однако такие действия физически влияют на процессор и нередко вызывают перегрев и выход из строя.

Выполнение инструкций

Инструкции хранятся в ОЗУ в последовательном порядке. Для гипотетического процессора инструкция состоит из кода операции и адреса памяти/регистра. Внутри управляющего устройства есть два регистра инструкций, в которые загружается код команды и адрес текущей исполняемой команды. Ещё в процессоре есть дополнительные регистры, которые хранят в себе последние 4 бита выполненных инструкций.

Ниже рассмотрен пример набора команд, который суммирует два числа:

LOAD_A 8. Это команда сохраняет в ОЗУ данные, скажем,<1100 1000>. Первые 4 бита — код операции. Именно он определяет инструкцию. Эти данные помещаются в регистры инструкций УУ. Команда декодируется в инструкциюload_A— поместить данные1000(последние 4 бита команды) в регистрA.LOAD_B 2. Ситуация, аналогичная прошлой. Здесь помещается число 2 (0010) в регистрB.ADD B A. Команда суммирует два числа (точнее прибавляет значение регистраBв регистрA). УУ сообщает АЛУ, что нужно выполнить операцию суммирования и поместить результат обратно в регистрA.STORE_A 23. Сохраняем значение регистраAв ячейку памяти с адресом23.

Вот такие операции нужны, чтобы сложить два числа.

Шина

Все данные между процессором, регистрами, памятью и I/O-устройствами (устройствами ввода-вывода) передаются по шинам. Чтобы загрузить в память только что обработанные данные, процессор помещает адрес в шину адреса и данные в шину данных. Потом нужно дать разрешение на запись на шине управления.

Кэш

У процессора есть механизм сохранения инструкций в кэш. Как мы выяснили ранее, за секунду процессор может выполнить миллиарды инструкций. Поэтому если бы каждая инструкция хранилась в ОЗУ, то её изъятие оттуда занимало бы больше времени, чем её обработка. Поэтому для ускорения работы процессор хранит часть инструкций и данных в кэше.

Если данные в кэше и памяти не совпадают, то они помечаются грязными битами (англ. dirty bit).

Поток инструкций

Современные процессоры могут параллельно обрабатывать несколько команд. Пока одна инструкция находится в стадии декодирования, процессор может успеть получить другую инструкцию.

Однако такое решение подходит только для тех инструкций, которые не зависят друг от друга.

Если процессор многоядерный, это означает, что фактически в нём находятся несколько отдельных процессоров с некоторыми общими ресурсами, например кэшем.

Если хотите узнать о процессорах больше, посмотрите, какие бывают популярные архитектуры: CISC, RISC, MISC и другие и виды.

Перевод статьи «How does a CPU work?»

An instruction is a set of codes that the computer processor can understand. The code is

usually in 1s and 0s, or machine language. It contains instructions or tasks that control

the movement of bits and bytes within the processor.

Example of some instruction sets −

-

ADD − Add two numbers together.

-

JUMP − Jump to designated RAM address.

-

LOAD − Load information from RAM to the CPU.

Types of Instruction Set

Generally, there are two types of instruction set used in computers.

Reduced Instruction set Computer (RISC)

A number of computer designers recommended that computers use fewer instructions

with simple constructs so that they can be executed much faster within the CPU without

having to use memory as often. This type of computer is called a Reduced Instruction

Set Computer.

The concept of RISC involves an attempt to reduce execution time by simplifying the

instruction set of computers.

Characteristics of RISC

The characteristics of RISC are as follows −

-

Relatively few instructions.

-

Relatively few addressing modes.

-

Memory access limited to load and store instructions.

-

All operations done within the register of the CPU.

-

Single-cycle instruction execution.

-

Fixed length, easily decoded instruction format.

-

Hardwired rather than micro programmed control.

A characteristic of RISC processors’ ability is to execute one instruction per clock cycle.

This is done by overlapping the fetch, decode and execute phases of two or three

instructions by using a procedure referred as pipelining.

Complex Instruction Set Computer (CISC)

CISC is a computer where a single instruction can perform numerous low-level

operations like a load from memory and a store from memory, etc. The CISC attempts to minimize the number of instructions per program but at the cost of an increase in the

number of cycles per instruction.

The design of an instruction set for a computer must take into consideration not only

machine language constructs but also the requirements imposed on the use of high level

programming languages.

The goal of CISC is to attempt to provide a single machine instruction for each statement

that is written in a high level language.

Characteristics of CISC

The characteristics of CISC are as follows −

-

A large number of instructions typically from 100 to 250 instructions.

-

Some instructions that perform specialized tasks and are used infrequently.

-

A large variety of addressing modes- typically from 5 to 20 different modes.

-

Variable length instruction formats.

-

Instructions that manipulate operands in memory.

Example

For performing an ADD operation, CISC will execute a single ADD command which will

execute all the required load and store operations.

RISC will execute each operation for loading data from memory, adding values and

storing data back to memory using different low-level instructions.

Процессоры миллионов компьютеров по всему миру знают только одно — непрерывно выполнять инструкции. А что такое инструкция? Читай дальше что бы узнать.

Что такое инструкция?

Инструкция — это минимальная единица программы, которая сообщает ЦП что делать с помощью серии инструкций, которые выполняются последовательно. Каждая инструкция представляет собой количество битов в двоичном коде, который разделен на три разные части:

- Биты инструкций: эти биты указывают, какую инструкцию будет выполнять ЦП, и поэтому путь, по которому инструкция будет следовать для выполнения, также называется кодом операции.

- Биты адресации: указывают, по какому адресу памяти хранятся данные.

- Биты режима: биты режима указывают, как выполняется инструкция, они используются, когда есть несколько способов выполнить инструкцию или есть разные условия.

Если вы хотите узнать, как процессор выполняет инструкции, мы рекомендуем статью » Вот как ваш процессор выполняет инструкции, которые дает ему программное обеспечение ”В HardZone, на том же сайте.

Инструкции по адресации

В зависимости от того, где находятся данные, у нас могут быть разные варианты одного и того же типа инструкций, способ, которым процессор получает доступ к данным, называется режимом адресации.

- Немедленная адресация используется, когда данные представляют собой одну и ту же инструкцию, в этом случае данные хранятся в регистре или внутренней памяти процессора, которые будут выполняться оттуда.

- Второй тип адресации — прямая, когда программа указывает адрес памяти, в котором находятся данные.

- Третий тип адресации — косвенный, который дает нам адрес, по которому находится адрес памяти, в котором находятся данные.

Следует уточнить, что некоторые инструкции не имеют режима адресации, поскольку они не требуют данных для выполнения.

Типы инструкций в ЦП

Вот краткое изложение наиболее распространенных инструкций, используемых различными процессорами. Эти инструкции являются общими для всех регистров и наборов инструкций, независимо от того, являются ли они x86, ARM, MIPS, PowerPC и так далее. Также не имеет значения, является ли набор инструкций RISC или CISC.

- Арифметические манипуляции инструкции — это те, которые выполняют операции математической обработки, такие как сложение, вычитание, умножение и деление. А также более сложные операции, такие как тригонометрические формулы, квадратные корни, степени.

- Наблюдения и советы этой статьи мы подготовили на основании опыта команды логические инструкции — это второй тип инструкций, выполняемых ALU, на самом деле они представляют собой двоичные операции, имитирующие работу логических вентилей. То есть AND, OR, XOR, NAND, NOR, XNOR и NOT.

- Инструкции по манипулированию битами основаны на манипулировании битами идемной строки с помощью таких инструкций, как сдвиг бита влево или вправо, изменение порядка или их переключение.

- Инструкции по перемещению данных отвечает за перемещение данных из одной части памяти в другую, из одной памяти в другую, из процессора в память и из памяти в процессор.

- Инструкции по управлению программой те, которые активируются при выполнении определенных условий, таких как

- Наблюдения и советы этой статьи мы подготовили на основании опыта команды инструкции по переходу — это те, которые указывают, что программа переходит не к следующему адресу памяти, а к конкретному адресу памяти, который отмечен инструкцией перехода.

Типы данных и множественность инструкций

Потому что сегодня ЦП может работать с разными типами данных, например с целыми числами и с плавающей запятой. Некоторые арифметические инструкции часто дублируются для набора команд с плавающей запятой. Существуют также векторные инструкции, такие как наборы инструкций AVX или также известные как инструкции SIMD, которые работают с несколькими операндами одновременно.

Поскольку эти инструкции выполняются в разных единицах, они в конечном итоге требуют разных битов инструкций, а это означает, что добавление новых типов данных в процессор означает во многих случаях значительное увеличение набора инструкций, их сложности. . а также часть, которая декодирует и выполняет их на ЦП.

Приветствую! Далеко не все пользователи задумываются, как конкретно работает процессор и как ему удаётся работать с программами. И это, впрочем, и не нужно знать, так как видеть результат этой работы вполне достаточно. Но иногда возникает проблема, когда ЦП просто не может справиться с каким-нибудь ПО или что бывает даже чаще, игрой.

Причиной этого могут являться неподходящие характеристики ПК, а среди них иногда упоминается и недостаток инструкций процессора, само существование которых может вызывать озадаченность. А ведь инструкции процессора это именно то, что и позволяет ему работать с разными программами. Поэтому о них и поговорим далее.

Для чего нужны инструкции в процессорах

У термина «инструкция» здесь нет никакого особого значения, это всё так же некоторая последовательность действий, которую нужно выполнить для получения результата.

А так как обработка данных — это основная задача ЦП, они все используют наборы заложенных команд для выполнения различных операций с информацией. Здесь нужно учитывать, что любая программа, от ОС до игры — это тоже совокупность команд, и когда ЦП выполняет инструкции, которые нужны программе для работы, всё складывается, и вы получаете результаты.

Если команд нет или их набор в неподходящей версии, с выполнением программы будут трудности. Звучит просто, но на самом деле система сложнее, просто я делаю допущения для вашего удобства.

Пакет инструкций, поддерживаемых процессором, закладываются в него изначально, поэтому поменять вы его не сможете. Разве что купив новый, более мощный ЦП.

Какие наборы инструкций существуют и чем отличаются

Условно команды можно разделить на две большие группы — базовые и дополнительные. Базовые нужны для выполнения основных операций, которые и заставляют CPU работать, дополнительные — для особых задач и оптимизации работы ЦП.

Команды общего назначения выполняют универсальные арифметические, логические, информационные задачи, а также те, что связаны с переносом данных и т. д. То, какие инструкции может выполнять ваш ЦП, зависит от его архитектуры, чем она лучше, тем команд больше. А вот разрядность CPU, например, влияет на то, как много команд одновременно получится выполнить.

Базовые команды общие для всех процессоров, так что вам достаточно знать только архитектуру. А дополнительные различаются в зависимости от производителя CPU и версии, так как меняются чаще, чем фундаментальные.

Например, вы можете увидеть, что ваш ЦП поддерживает MMX. Это набор, который пригодится для ускоренной обработки фото, аудио и видео. Он был разработан Intel ещё в конце 90-х.

SSE обеспечивает устройствам от Intel быстродействие, когда одни и те же данные нужно использовать в разных вычислениях.

SSE2 необходима всему современному ПО, без этих команд у вас не будут работать ни версии Windows, начиная с 8, ни большинство программ. Например, даже браузеры от Яндекса и Google не получится запустить.

SSE3 пригодится для обработки графической, аудио и видеоинформации. Есть и другие версии SSE, каждая из которых имеет больше команд, чем предыдущая.

AES, которую также можно встретить в Intel, представляет собой расширение команд ЦП для ускорения работы программ и их большей защищённости. Название связано с алгоритмом шифрования Advanced Encryption Standard.

AVX, разработанный Intel в 2008, влияет как на вычислительные, так и мультимедийные возможности ЦП. А вот следующая версия, AVX 2, даёт прирост производительности при работе с фото, видео, аудио, программами распознавания голоса и т. д.

FMA ускоряет операции умножения и сложения с плавающей запятой, которые выполняются командами общего назначения.

А VT-x расширяет возможности работы ПК с виртуальными машинами.

Как вы могли заметить, инструкции, описанные выше, актуальны для Intel. А вот, например, для AMD есть свои:

- SenseMI — в первый раз использовался в Ryzen, прогнозирует программный код для лучшей производительности ЦП.

- AMD CoolCore — реализует временное отключение блоков процессора для снижения энергопотребления.

- AMD CoolSpeed — защищает ЦП от перегрева.

- AMD Enduro — ещё одна технология для энергосбережения.

Есть и универсальные технологии, вроде BMI или F16C.

Те наборы команд, которые я описал, лишь малая часть того, что вы можете встретить. Но я думаю и их достаточно, чтобы понять суть. Обращайте на них внимание в характеристиках программ, а в особенности игр, перед покупкой.

Как узнать какие инструкции поддерживает процессор

Вы наверняка уже задались вопросом, как узнать какие инструкции поддерживает процессор компьютера, и я могу на него ответить.

Для начала, вы можете найти список команд ЦП, просто сделав поисковый запрос. Зачастую нужная информация найдётся на официальных сайтах производителей ЦП. Если не получится, то на сайтах, посвящённых компьютерам, нередко есть целый раздел, где можно ввести название устройства в поиск и прочесть расширенные данные о нём. О наборах команд обязательно что-то будет.

Если не хотите искать, есть и другой способ, как посмотреть количество инструкций ЦП. Например, вы можете воспользоваться CPU-Z или другими подобными программами. В CPU-Z нужная информация будет в блоке «Instructions» прямо в первом окне. Скопируйте список и просто сравните его с требованиями для игр или ПО. Всё равно если вы не увидите подходящих версий, поможет только замена устройства.

На самом деле, инструкции процессора — не такая простая тема. Но описанного выше, думаю, вполне достаточно, чтобы иметь общее представление о том, что такое инструкции процессора и откуда их взять. Подробнее о других особенностях ЦП и остальных компонентах компьютеров поговорим в другой раз, и чтобы не пропустить новые публикации, нужно лишь подписаться на мои социальные сети, где новости всегда самые свежие. Увидимся!

С уважением, автор блога Андрей Андреев.

Устройство процессора.

Процессор – это

основное устройство ЭВМ, выполняющее

логические и арифметические операции,

и осуществляющее управление всеми

компонентами ЭВМ. Процессор представляет

собой миниатюрную тонкую кремниевую

пластинку прямоугольной формы, на

которой размещается огромное количество

транзисторов, реализующих все функции,

выполняемые процессором. Кремневая

пластинка – очень хрупкая, а так как ее

любое повреждение приведет к выходу из

строя процессора, то она помещается в

пластиковый или керамический корпус.

Содержание.

1.

Введение

2.

Ядро процессора

2.1.

Принцип работы ядра процессора

2.2.

Способы повышения производительности

ядра процессора

2.2.1.

Конвейеризация

2.2.2.

Суперскалярность

2.2.3.

Параллельная обработка данных

2.2.4.

Технология Hyper-threading

2.2.5.

Технология Turbo Boost.

2.2.6.

Эффективность выполнения команд.

2.3

Способы снижения энергопотребления

ядра процессора

3.

КЭШ-память

1. Введение.

Современный

процессор – это сложное и высокотехнологическое

устройство, включающее в себя все самые

последние достижения в области

вычислительной техники и сопутствующих

областей науки.

Большинство

современных процессоров состоит из:

-

одного или

нескольких ядер, осуществляющих

выполнение всех инструкций; -

нескольких уровней

КЭШ-памяти (обычно, 2 или три уровня),

ускоряющих взаимодействие процессора

с ОЗУ; -

контроллера ОЗУ;

-

контроллера

системной шины (DMI, QPI, HT и т.д.);

И характеризуется

следующими параметрами:

-

типом микроархитектуры;

-

тактовой частотой;

-

набором выполняемых

команд; -

количеством

уровней КЭШ-памяти и их объемом; -

типом и скоростью

системной шины; -

размерами

обрабатываемых слов; -

наличием или

отсутствием встроенного контроллера

памяти; -

типом поддерживаемой

оперативной памяти; -

объемом адресуемой

памяти; -

наличием или

отсутствием встроенного графического

ядра; -

энергопотреблением.

Упрощенная

структурная схема современного

многоядерного процессора представлена

на рисунке 1.

Начнем обзор

устройства процессора с его основной

части – ядра.

2. Ядро процессора.

Ядро процессора

– это его основная часть, содержащая

все функциональные блоки и осуществляющая

выполнение всех логических и арифметических

операций.

На рисунке 1

приведена структурная схема устройства

ядра процессора. Как видно на рисунке,

каждое ядро процессора состоит из

нескольких функциональных блоков:

-

блока выборки

инструкций; -

блоков декодирования

инструкций; -

блоков выборки

данных; -

управляющего

блока; -

блоков выполнения

инструкций; -

блоков сохранения

результатов; -

блока работы с

прерываниями; -

ПЗУ, содержащего

микрокод; -

набора регистров;

-

счетчика команд.

Блок

выборки инструкций осуществляет

считывание инструкций по адресу,

указанному в счетчике команд. Обычно,

за такт он считывает несколько инструкций.

Количество считываемых инструкций

обусловлено количеством блоков

декодирования, так как необходимо на

каждом такте работы максимально загрузить

блоки декодирования. Для того чтобы

блок выборки инструкций работал

оптимально, в ядре процессора имеется

предсказатель переходов.

Предсказатель

переходов пытается

определить, какая последовательность

команд будет выполняться после совершения

перехода. Это необходимо, чтобы после

условного перехода максимально нагрузить

конвейер ядра процессора.

Блоки

декодирования,

как понятно из названия, – это блоки,

которые занимаются декодированием

инструкций, т.е. определяют, что надо

сделать процессору, и какие дополнительные

данные нужны для выполнения инструкции.

Задача эта для большинства современных

коммерческих процессоров, построенных

на базе концепции CISC, – очень сложная.

Дело в том, что длина инструкций и

количество операндов – нефиксированные,

и это сильно усложняет жизнь разработчикам

процессоров и делает процесс декодирования

нетривиальной задачей.

Часто отдельные

сложные команды приходится заменять

микрокодом – серией простых инструкций,

в совокупности выполняющих то же

действие, что и одна сложная инструкция.

Набор микрокода прошит в ПЗУ, встроенном

в процессоре. К тому же микрокод упрощает

разработку процессора, так как отпадает

надобность в создании сложноустроенных

блоков ядра для выполнения отдельных

команд, да и исправить микрокод гораздо

проще, чем устранить ошибку в

функционировании блока.

В современных

процессорах, обычно, бывает 2-4 блока

декодирования инструкций, например, в

процессорах Intel Core 2 каждое ядро содержит

по два таких блока.

Блоки

выборки данных осуществляют

выборку данных из КЭШ-памяти или ОЗУ,

необходимых для выполнения текущих

инструкций. Обычно, каждое процессорное

ядро содержит несколько блоков выборки

данных. Например, в процессорах Intel Core

используется по два блока выборки данных

для каждого ядра.

Управляющий

блок на

основании декодированных инструкций

управляет работой блоков выполнения

инструкций, распределяет нагрузку между

ними, обеспечивает своевременное и

верное выполнение инструкций. Это один

из наиболее важных блоков ядра процессора.

Блоки

выполнения инструкций включают

в себя несколько разнотипных блоков:

ALU – арифметическое

логическое устройство;

FPU – устройство

по выполнению операций с плавающей

точкой;

Блоки для обработки

расширения наборов инструкций.

Дополнительные инструкции используются

для ускорения обработки потоков данных,

шифрования и дешифрования, кодирования

видео и так далее. Для этого в ядро

процессора вводят дополнительные

регистры и наборы логики. На данный

момент наиболее популярными расширениями

наборов инструкция являются:

MMX (Multimedia Extensions) –

набор инструкций, разработанный компанией

Intel, для ускорения кодирования и

декодирования потоковых аудио и

видео-данных;

SSE (Streaming SIMD

Extensions) – набор инструкций, разработанный

компанией Intel, для выполнения одной и

той же последовательности операций над

множеством данных с распараллеливанием

вычислительного процесса. Наборы команд

постоянно совершенствуются, и на данный

момент имеются ревизии: SSE, SSE2, SSE3, SSSE3,

SSE4;

ATA (Application Targeted

Accelerator) – набор инструкций, разработанный

компанией Intel, для ускорения работы

специализированного программного

обеспечения и снижения энергопотребления

при работе с такими программами. Эти

инструкции могут использоваться,

например, при расчете контрольных сумм

или поиска данных;

3DNow – набор

инструкций, разработанный компанией

AMD, для расширения возможностей набора

инструкций MMX;

AES (Advanced Encryption

Standard) – набор инструкций, разработанный

компанией Intel, для ускорения работы

приложений, использующих шифрование

данных по одноименному алгоритму.

Блок

сохранения результатов обеспечивает

запись результата выполнения инструкции

в ОЗУ по адресу, указанному в обрабатываемой

инструкции.

Блок

работы с прерываниями. Работа

с прерываниями – одна из важнейших

задач процессора, позволяющая ему

своевременно реагировать на события,

прерывать ход работы программы и

выполнять требуемые от него действия.

Благодаря наличию прерываний, процессор

способен к псевдопараллельной работе,

т.е. к, так называемой, многозадачности.

Обработка прерываний

происходит следующим образом. Процессор

перед началом каждого цикла работы

проверяет наличие запроса на прерывание.

Если есть прерывание для обработки,

процессор сохраняет в стек адрес

инструкции, которую он должен был

выполнить, и данные, полученные после

выполнения последней инструкции, и

переходит к выполнению функции обработки

прерывания.

После окончания

выполнения функции обработки прерывания,

из стека считываются сохраненные в него

данные, и процессор возобновляет

выполнение восстановленной задачи.

Регистры –

сверхбыстрая оперативная память (доступ

к регистрам в несколько раз быстрее

доступа к КЭШ-памяти) небольшого объема

(несколько сотен байт), входящая в состав

процессора, для временного хранения

промежуточных результатов выполнения

инструкций. Регистры процессора делятся

на два типа: регистры общего назначения

и специальные регистры.

Регистры общего

назначения используются при выполнении

арифметических и логических операций,

или специфических операций дополнительных

наборов инструкций (MMX, SSE и т.д.).

Регистры специального

назначения содержат системные данные,

необходимые для работы процессора. К

таким регистрам относятся, например,

регистры управления, регистры системных

адресов, регистры отладки и т.д. Доступ

к этим регистрам жестко регламентирован.

Счетчик

команд –

регистр, содержащий адрес команды,

которую процессор начнет выполнять на

следующем такте работы.

Соседние файлы в папке ТСИ

- #

- #

- #

- #

- #

- #

In computer science, an instruction set architecture (ISA), also called computer architecture, is an abstract model of a computer. A device that executes instructions described by that ISA, such as a central processing unit (CPU), is called an implementation.

In general, an ISA defines the supported instructions, data types, registers, the hardware support for managing main memory, fundamental features (such as the memory consistency, addressing modes, virtual memory), and the input/output model of a family of implementations of the ISA.

An ISA specifies the behavior of machine code running on implementations of that ISA in a fashion that does not depend on the characteristics of that implementation, providing binary compatibility between implementations. This enables multiple implementations of an ISA that differ in characteristics such as performance, physical size, and monetary cost (among other things), but that are capable of running the same machine code, so that a lower-performance, lower-cost machine can be replaced with a higher-cost, higher-performance machine without having to replace software. It also enables the evolution of the microarchitectures of the implementations of that ISA, so that a newer, higher-performance implementation of an ISA can run software that runs on previous generations of implementations.

If an operating system maintains a standard and compatible application binary interface (ABI) for a particular ISA, machine code will run on future implementations of that ISA and operating system. However, if an ISA supports running multiple operating systems, it does not guarantee that machine code for one operating system will run on another operating system, unless the first operating system supports running machine code built for the other operating system.

An ISA can be extended by adding instructions or other capabilities, or adding support for larger addresses and data values; an implementation of the extended ISA will still be able to execute machine code for versions of the ISA without those extensions. Machine code using those extensions will only run on implementations that support those extensions.

The binary compatibility that they provide makes ISAs one of the most fundamental abstractions in computing.

Overview[edit]

An instruction set architecture is distinguished from a microarchitecture, which is the set of processor design techniques used, in a particular processor, to implement the instruction set. Processors with different microarchitectures can share a common instruction set. For example, the Intel Pentium and the AMD Athlon implement nearly identical versions of the x86 instruction set, but they have radically different internal designs.

The concept of an architecture, distinct from the design of a specific machine, was developed by Fred Brooks at IBM during the design phase of System/360.

Prior to NPL [System/360], the company’s computer designers had been free to honor cost objectives not only by selecting technologies but also by fashioning functional and architectural refinements. The SPREAD compatibility objective, in contrast, postulated a single architecture for a series of five processors spanning a wide range of cost and performance. None of the five engineering design teams could count on being able to bring about adjustments in architectural specifications as a way of easing difficulties in achieving cost and performance objectives.[1]: p.137

Some virtual machines that support bytecode as their ISA such as Smalltalk, the Java virtual machine, and Microsoft’s Common Language Runtime, implement this by translating the bytecode for commonly used code paths into native machine code. In addition, these virtual machines execute less frequently used code paths by interpretation (see: Just-in-time compilation). Transmeta implemented the x86 instruction set atop VLIW processors in this fashion.

Classification of ISAs[edit]

An ISA may be classified in a number of different ways. A common classification is by architectural complexity. A complex instruction set computer (CISC) has many specialized instructions, some of which may only be rarely used in practical programs. A reduced instruction set computer (RISC) simplifies the processor by efficiently implementing only the instructions that are frequently used in programs, while the less common operations are implemented as subroutines, having their resulting additional processor execution time offset by infrequent use.[2]

Other types include very long instruction word (VLIW) architectures, and the closely related long instruction word (LIW) and[citation needed] explicitly parallel instruction computing (EPIC) architectures. These architectures seek to exploit instruction-level parallelism with less hardware than RISC and CISC by making the compiler responsible for instruction issue and scheduling.[3]

Architectures with even less complexity have been studied, such as the minimal instruction set computer (MISC) and one-instruction set computer (OISC). These are theoretically important types, but have not been commercialized.[4][5]

Instructions[edit]

Machine language is built up from discrete statements or instructions. On the processing architecture, a given instruction may specify:

- opcode (the instruction to be performed) e.g. add, copy, test

- any explicit operands:

-

- registers

- literal/constant values

- addressing modes used to access memory

More complex operations are built up by combining these simple instructions, which are executed sequentially, or as otherwise directed by control flow instructions.

Instruction types[edit]

Examples of operations common to many instruction sets include:

Data handling and memory operations[edit]

- Set a register to a fixed constant value.

- Copy data from a memory location or a register to a memory location or a register (a machine instruction is often called move; however, the term is misleading). They are used to store the contents of a register, the contents of another memory location or the result of a computation, or to retrieve stored data to perform a computation on it later. They are often called load and store operations.

- Read and write data from hardware devices.

Arithmetic and logic operations[edit]

- Add, subtract, multiply, or divide the values of two registers, placing the result in a register, possibly setting one or more condition codes in a status register.[6]

- increment, decrement in some ISAs, saving operand fetch in trivial cases.

- Perform bitwise operations, e.g., taking the conjunction and disjunction of corresponding bits in a pair of registers, taking the negation of each bit in a register.

- Compare two values in registers (for example, to see if one is less, or if they are equal).

- Floating-point instructions for arithmetic on floating-point numbers.[6]

Control flow operations[edit]

- Branch to another location in the program and execute instructions there.

- Conditionally branch to another location if a certain condition holds.

- Indirectly branch to another location.

- Call another block of code, while saving the location of the next instruction as a point to return to.

Coprocessor instructions[edit]

- Load/store data to and from a coprocessor or exchanging with CPU registers.

- Perform coprocessor operations.

Complex instructions[edit]

Processors may include «complex» instructions in their instruction set. A single «complex» instruction does something that may take many instructions on other computers. Such instructions are typified by instructions that take multiple steps, control multiple functional units, or otherwise appear on a larger scale than the bulk of simple instructions implemented by the given processor. Some examples of «complex» instructions include:

- transferring multiple registers to or from memory (especially the stack) at once

- moving large blocks of memory (e.g. string copy or DMA transfer)

- complicated integer and floating-point arithmetic (e.g. square root, or transcendental functions such as logarithm, sine, cosine, etc.)

- SIMD instructions, a single instruction performing an operation on many homogeneous values in parallel, possibly in dedicated SIMD registers

- performing an atomic test-and-set instruction or other read-modify-write atomic instruction

- instructions that perform ALU operations with an operand from memory rather than a register

Complex instructions are more common in CISC instruction sets than in RISC instruction sets, but RISC instruction sets may include them as well. RISC instruction sets generally do not include ALU operations with memory operands, or instructions to move large blocks of memory, but most RISC instruction sets include SIMD or vector instructions that perform the same arithmetic operation on multiple pieces of data at the same time. SIMD instructions have the ability of manipulating large vectors and matrices in minimal time. SIMD instructions allow easy parallelization of algorithms commonly involved in sound, image, and video processing. Various SIMD implementations have been brought to market under trade names such as MMX, 3DNow!, and AltiVec.

Instruction encoding[edit]

On traditional architectures, an instruction includes an opcode that specifies the operation to perform, such as add contents of memory to register—and zero or more operand specifiers, which may specify registers, memory locations, or literal data. The operand specifiers may have addressing modes determining their meaning or may be in fixed fields. In very long instruction word (VLIW) architectures, which include many microcode architectures, multiple simultaneous opcodes and operands are specified in a single instruction.

Some exotic instruction sets do not have an opcode field, such as transport triggered architectures (TTA), only operand(s).

Most stack machines have «0-operand» instruction sets in which arithmetic and logical operations lack any operand specifier fields; only instructions that push operands onto the evaluation stack or that pop operands from the stack into variables have operand specifiers. The instruction set carries out most ALU actions with postfix (reverse Polish notation) operations that work only on the expression stack, not on data registers or arbitrary main memory cells. This can be very convenient for compiling high-level languages, because most arithmetic expressions can be easily translated into postfix notation.[7]

Conditional instructions often have a predicate field—a few bits that encode the specific condition to cause an operation to be performed rather than not performed. For example, a conditional branch instruction will transfer control if the condition is true, so that execution proceeds to a different part of the program, and not transfer control if the condition is false, so that execution continues sequentially. Some instruction sets also have conditional moves, so that the move will be executed, and the data stored in the target location, if the condition is true, and not executed, and the target location not modified, if the condition is false. Similarly, IBM z/Architecture has a conditional store instruction. A few instruction sets include a predicate field in every instruction; this is called branch predication.

Number of operands[edit]

Instruction sets may be categorized by the maximum number of operands explicitly specified in instructions.

(In the examples that follow, a, b, and c are (direct or calculated) addresses referring to memory cells, while reg1 and so on refer to machine registers.)

C = A+B

- 0-operand (zero-address machines), so called stack machines: All arithmetic operations take place using the top one or two positions on the stack:[8]

push a,push b,add,pop c.C = A+Bneeds four instructions.[9] For stack machines, the terms «0-operand» and «zero-address» apply to arithmetic instructions, but not to all instructions, as 1-operand push and pop instructions are used to access memory.

- 1-operand (one-address machines), so called accumulator machines, include early computers and many small microcontrollers: most instructions specify a single right operand (that is, constant, a register, or a memory location), with the implicit accumulator as the left operand (and the destination if there is one):

load a,add b,store c.C = A+Bneeds three instructions.[9]

- 2-operand — many CISC and RISC machines fall under this category:

- CISC —

move Ato C; thenadd Bto C.C = A+Bneeds two instructions. This effectively ‘stores’ the result without an explicit store instruction.

- CISC — Often machines are limited to one memory operand per instruction:

load a,reg1;add b,reg1;store reg1,c; This requires a load/store pair for any memory movement regardless of whether theaddresult is an augmentation stored to a different place, as inC = A+B, or the same memory location:A = A+B.C = A+Bneeds three instructions.

- RISC — Requiring explicit memory loads, the instructions would be:

load a,reg1;load b,reg2;add reg1,reg2;store reg2,c.C = A+Bneeds four instructions.

- CISC —

- 3-operand, allowing better reuse of data:[10]

- CISC — It becomes either a single instruction:

add a,b,cC = A+Bneeds one instruction.

- CISC — Or, on machines limited to two memory operands per instruction,

move a,reg1;add reg1,b,c;C = A+Bneeds two instructions.

- RISC — arithmetic instructions use registers only, so explicit 2-operand load/store instructions are needed:

load a,reg1;load b,reg2;add reg1+reg2->reg3;store reg3,c;C = A+Bneeds four instructions.- Unlike 2-operand or 1-operand, this leaves all three values a, b, and c in registers available for further reuse.[10]

- CISC — It becomes either a single instruction:

- more operands—some CISC machines permit a variety of addressing modes that allow more than 3 operands (registers or memory accesses), such as the VAX «POLY» polynomial evaluation instruction.

Due to the large number of bits needed to encode the three registers of a 3-operand instruction, RISC architectures that have 16-bit instructions are invariably 2-operand designs, such as the Atmel AVR, TI MSP430, and some versions of ARM Thumb. RISC architectures that have 32-bit instructions are usually 3-operand designs, such as the ARM, AVR32, MIPS, Power ISA, and SPARC architectures.

Each instruction specifies some number of operands (registers, memory locations, or immediate values) explicitly. Some instructions give one or both operands implicitly, such as by being stored on top of the stack or in an implicit register. If some of the operands are given implicitly, fewer operands need be specified in the instruction. When a «destination operand» explicitly specifies the destination, an additional operand must be supplied. Consequently, the number of operands encoded in an instruction may differ from the mathematically necessary number of arguments for a logical or arithmetic operation (the arity). Operands are either encoded in the «opcode» representation of the instruction, or else are given as values or addresses following the opcode.

Register pressure[edit]

Register pressure measures the availability of free registers at any point in time during the program execution. Register pressure is high when a large number of the available registers are in use; thus, the higher the register pressure, the more often the register contents must be spilled into memory. Increasing the number of registers in an architecture decreases register pressure but increases the cost.[11]

While embedded instruction sets such as Thumb suffer from extremely high register pressure because they have small register sets, general-purpose RISC ISAs like MIPS and Alpha enjoy low register pressure. CISC ISAs like x86-64 offer low register pressure despite having smaller register sets. This is due to the many addressing modes and optimizations (such as sub-register addressing, memory operands in ALU instructions, absolute addressing, PC-relative addressing, and register-to-register spills) that CISC ISAs offer.[12]

Instruction length[edit]

The size or length of an instruction varies widely, from as little as four bits in some microcontrollers to many hundreds of bits in some VLIW systems. Processors used in personal computers, mainframes, and supercomputers have minimum instruction sizes between 8 and 64 bits. The longest possible instruction on x86 is 15 bytes (120 bits).[13] Within an instruction set, different instructions may have different lengths. In some architectures, notably most reduced instruction set computers (RISC), instructions are a fixed length, typically corresponding with that architecture’s word size. In other architectures, instructions have variable length, typically integral multiples of a byte or a halfword. Some, such as the ARM with Thumb-extension have mixed variable encoding, that is two fixed, usually 32-bit and 16-bit encodings, where instructions cannot be mixed freely but must be switched between on a branch (or exception boundary in ARMv8).

Fixed-length instructions are less complicated to handle than variable-length instructions for several reasons (not having to check whether an instruction straddles a cache line or virtual memory page boundary,[10] for instance), and are therefore somewhat easier to optimize for speed.

Code density[edit]

In early 1960s computers, main memory was expensive and very limited, even on mainframes. Minimizing the size of a program to make sure it would fit in the limited memory was often central. Thus the size of the instructions needed to perform a particular task, the code density, was an important characteristic of any instruction set. It remained important on the initially-tiny memories of minicomputers and then microprocessors. Density remains important today, for smartphone applications, applications downloaded into browsers over slow Internet connections, and in ROMs for embedded applications. A more general advantage of increased density is improved effectiveness of caches and instruction prefetch.

Computers with high code density often have complex instructions for procedure entry, parameterized returns, loops, etc. (therefore retroactively named Complex Instruction Set Computers, CISC). However, more typical, or frequent, «CISC» instructions merely combine a basic ALU operation, such as «add», with the access of one or more operands in memory (using addressing modes such as direct, indirect, indexed, etc.). Certain architectures may allow two or three operands (including the result) directly in memory or may be able to perform functions such as automatic pointer increment, etc. Software-implemented instruction sets may have even more complex and powerful instructions.

Reduced instruction-set computers, RISC, were first widely implemented during a period of rapidly growing memory subsystems. They sacrifice code density to simplify implementation circuitry, and try to increase performance via higher clock frequencies and more registers. A single RISC instruction typically performs only a single operation, such as an «add» of registers or a «load» from a memory location into a register. A RISC instruction set normally has a fixed instruction length, whereas a typical CISC instruction set has instructions of widely varying length. However, as RISC computers normally require more and often longer instructions to implement a given task, they inherently make less optimal use of bus bandwidth and cache memories.

Certain embedded RISC ISAs like Thumb and AVR32 typically exhibit very high density owing to a technique called code compression. This technique packs two 16-bit instructions into one 32-bit word, which is then unpacked at the decode stage and executed as two instructions.[14]